# Marvell Socket-7 CPU Modules

User Guide

Doc. No. MV-L100047-10, Rev. E January 30, 2003

| Document                   | Document Status                                                                                                                                                                           |                                                                                                                                                                                                                          |  |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Advanced<br>Information    | This document contains design specifications for initial product development. Specifications may change without notice. Contact Marvell Field Application Engineers for more information. |                                                                                                                                                                                                                          |  |  |  |

| Preliminary<br>Information |                                                                                                                                                                                           | This document contains preliminary data, and a revision of this document will be published at a later date.  Specifications may change without notice. Contact Marvell Field Application Engineers for more information. |  |  |  |

| Final<br>Information       | This document contains specifications on a product that is in final release. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.  |                                                                                                                                                                                                                          |  |  |  |

| Revision Code              | :                                                                                                                                                                                         |                                                                                                                                                                                                                          |  |  |  |

| Preliminary                |                                                                                                                                                                                           | Technical Publication:                                                                                                                                                                                                   |  |  |  |

#### Preliminary Information

This document provides Preliminary information about the products described. All specifications described herein are based on design goals only. Do not use for final design. Visit the Marvell® web site at www.marvell.com or call 1-866-674-7253 for the latest information on Marvell products.

#### Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell makes no commitment either to update or to keep current the information contained in this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not notated Marvell products in these types of equipment or applications. The user should contact Marvell to obtain the latest specifications before finalizing a product design. Marvell assumes no responsibility, either for use of these products or for any infringements of patents and trademarks, or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Marvell. These products may include one or more optional functions. The user has the choice of implementing any particular optional function. Should the user choose to implement any of these optional functions, it is possible that the use could be subject to third party intellectual property rights are relevant to the intended use of these products and obtain licenses as appropriate under relevant intellectual property rights.

Marvell comprises Marvell Technology Group Ltd. (MTGL) and its subsidiaries, Marvell International Ltd. (MIL), Marvell Semiconductor, Inc. (MSI), Marvell Asia Pte Ltd. (MAPL), Marvell Japan K.K. (MJKK), Marvell Semiconductor Israel Ltd. (MSIL), and SysKonnect GmbH.

Copyright © 2003. Marvell. All rights reserved. Marvell logo, Moving Forward Faster, Alaska, and GalNet are registered trademarks of Marvell. Discovery, Fastwriter, GalTis, Horizon, Libertas, Link Street, NetGX, PHY Advantage, Prestera, Raising The Technology Bar, UniMAC, Virtual Cable Tester, and Yukon are trademarks of Marvell. All other trademarks are the property of their respective owners.

Marvell 700 First Avenue Sunnyvale, CA 94089 Phone: (408) 222 2500 Sales Fax: (408) 752 9029 Email commsales@marvell.com

# **Table of Contents**

| SEC | TION 1.   | Introduction                          | 7  |

|-----|-----------|---------------------------------------|----|

| 1.1 | Docume    | ntation Updates and Technical Support | 7  |

| SEC | TION 2.   | DB-MPC7455DDR-L3-S7                   | 8  |

| 2.1 | Overviev  | v                                     | 8  |

| 2.2 | Descripti | ion                                   | 9  |

| 2.3 | DB-MPC    | 7455DDR-L3-S7 Module Jumpers          | 9  |

| SEC | CTION 3.  | DB-SR71010-S7                         | 11 |

| 3.1 | Overviev  | v                                     | 11 |

| 3.2 | Descript  | ion                                   | 11 |

| 3.3 | DB-SR71   | 010-S7 Module Jumpers                 | 12 |

| SEC | TION 4.   | DB-IBM750CXE-S7                       | 13 |

| 4.1 | Overviev  | v                                     | 13 |

| 4.2 | Descript  | ion                                   | 13 |

| 4.3 | DB-IBM7   | 50CXe-S7 Module Jumpers               | 14 |

| SEC | TION 5.   | DB-IBM750FX-S7                        | 16 |

| 5.1 | Overviev  | v                                     | 16 |

| 5.2 | Descript  | ion                                   | 16 |

| 5.3 | DB-IBM7   | 50FX-S7 Module Jumpers                | 17 |

| SEC | CTION 6.  | DB-RM7000A/B-S7 MODULE                | 19 |

| 6.1 | Descript  | ion                                   | 19 |

| 6.2 | DB-RM70   | 000A/B-S7 Module Jumpers              | 20 |

| SEC | TION 7.   | DB-RM7000C                            | 24 |

| 7.1 | Descript  | ion                                   | 24 |

| 7.2 | DB-RM70   | 000C Module Jumpers                   | 25 |

| SEC | TION 8.   | DB-RM9000 Module   | 27 |

|-----|-----------|--------------------|----|

| 8.1 | Descripti | ion                | 27 |

| 8.2 | DB-RM90   | 000 Module Jumpers | 28 |

| 8.3 | DB-RM90   | 000 Restrictions   | 30 |

| SEC | TION 9.   | REVISION HISTORY   | 31 |

# **List of Tables**

| Table 1:  | DB-MPC7455DDR-L3-S7 Module Jumpers            | 9  |

|-----------|-----------------------------------------------|----|

| Table 2:  | DB-MPC7455DDR-L3-S7 Module Resistors and DPRs | 10 |

| Table 3:  | DB-SR71010-S7 Module Jumpers                  | 12 |

| Table 4:  | DB-SR71010-S7 Module Configuration Resistor   | 12 |

| Table 5:  | DB-IBM750CXe-S7 Module Jumpers                | 14 |

| Table 6:  | DB-IBM750CXe-S7 Module Resistors and DPRs     | 14 |

| Table 7:  | DB-IBM750FX-S7 Module Jumpers                 | 17 |

| Table 8:  | DB-IBM750FX-S7 Module Resistors and DPRs      | 17 |

| Table 9:  | DB-RM7000A/B-S7 Module Jumpers                | 20 |

| Table 10: | DB-RM7000A/B-S7 Module DPRs                   | 22 |

| Table 11: | DB-RM7000A/B-S7 Module Configuration Resistor | 23 |

| Table 12: | Vcc INT Voltage Resistor Configuration        | 23 |

| Table 13: | DB-RM7000C Module Jumpers                     | 25 |

| Table 14: | DB-RM7000C Module DPR                         | 25 |

| Table 15: | Vcc INT Voltage Resistor Configuration        | 26 |

| Table 16: | DB-RM9000 Module Jumpers                      | 28 |

| Table 17: | DB-RM9000 Module DPR                          | 29 |

| Table 18: | VCC INT Voltage Resistor Configuration        | 30 |

| Table 19: | Revision History                              | 31 |

# **List of Figures**

| Figure 1: | DB-MPC7455DDR-L3-S7 Module Components | ç  |

|-----------|---------------------------------------|----|

| Figure 2: | DB-SR71010-S7 Module Components       | 11 |

| Figure 3: | DB-IBM750CXe-S7 Module Components     | 13 |

| Figure 4: | DB-IBM750FX-S7 Module Components      | 16 |

| Figure 5: | DB-RM7000A/B-S7 Module Components     | 19 |

| Figure 6: | DB-RM7000C Module Components          | 24 |

| Figure 7: | DB-RM9000 Module Components           | 27 |

# **Section 1. Introduction**

The DB-64340/60 and DB-96340/60 Marvell® development boards incorporate a CPU socket compatible to the Socket-7 mechanism, which can accommodate various CPU modules.

This document describes following Socket-7 CPU modules:

| • | DB-MPC7455DDR-L3-S7 | Section 2 |

|---|---------------------|-----------|

| • | DB-SR71010-S7       | Section 3 |

| • | DB-IBM750CXe-S7     | Section 4 |

| • | DB-IBM750FX-S7      | Section 5 |

| • | DB-RM7000A/B-S7     | Section 6 |

| • | DB-RM7000C          | Section 7 |

| • | DB-RM9000           | Section 8 |

Each module has its own configuration settings when connected to the various Marvell development boards (backplanes).

### Note

These modules are equipped with a I<sup>2</sup>C 256 Byte General Purpose EEPROM for future use.

# 1.1 Documentation Updates and Technical Support

Marvell may have updated the documentation or software (if any) that was shipped with these modules. See the Marvell website at <a href="http://www.marvell.com">http://www.marvell.com</a> for the following information:

- Assembly map drawings

- Block diagrams

- Module schematics

- BOM

- Gerber files

- PLD equations

### Section 2. DB-MPC7455DDR-L3-S7

### 2.1 Overview

The DB-MPC7455DDR-L3-S7 is a CPU and L3 cache module. This module enables Marvell devices to operate with Motorola's MPC7455 CPU. The module plugs into the Socket-7 connector designed for it.

### Note

Due to instability of the HVREF power source, which is used as a reference voltage for the L3 clock, the DB-MPC7455DDR-L3-S7 module supports an **L3 cache** frequency of 166 MHz. This instability will be corrected in rev 2.0 of the board.

### Warnings

- · Make sure the CPU fan is connected to the power.

- If the fan does not work, the CPU may burn out and the system must be turned off.

The DB-MPC7455DDR-L3-S7 includes the following features:

- Up to 133 MHz CPU bus frequency

- Optional CPUs (Motorola's MPC7455)

- Onboard L3 cache (supports 2 MB of DDR SRAM L3 cache)

- Debug port (COP interface with standard 16-pin header)

# 2.2 Description

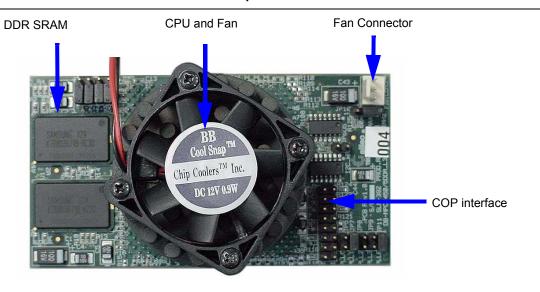

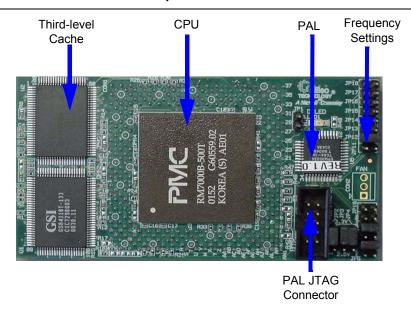

The DB-MPC7455DDR-L3-S7 module components are illustrated in Figure 1.

Figure 1: DB-MPC7455DDR-L3-S7 Module Components

# 2.3 DB-MPC7455DDR-L3-S7 Module Jumpers

Table 1 details the DB-MPC7455DDR-L3-S7 module jumpers.

Table 1: DB-MPC7455DDR-L3-S7 Module Jumpers

| Jumper                                               | Shipping Configuration                                                             | Assignment                                      | Description                                                                                                                                               |

|------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1, JP2,<br>JP3, JP4<br>(Vcc IO)                    | 1-2, 1-2<br>1-2, 1-2                                                               | CPU's Vcc I/O = 2.5V                            | The jumpers select the Vcc I/O that is supplied to the module. All four jumpers must be set to the same position. 1-2: Vcc I/O = 2.5V 2-3: Vcc I/O = 1.8V |

| JP5, JP7,<br>JP8, JP9,<br>JP11 (PLL0-3,<br>PLL_EXT), | NOTE: PLL[03] and PLL_EXT (JP11) are set according to the CPU's maximum frequency. | According to the CPU's maximum frequency.       | For each jumper: In: 0 Out: 1 The frequency setting table can be found in Motorola's specs.                                                               |

| JP10                                                 | 2-3                                                                                | MPX bus mode                                    | The jumper selects the CPU's bus mode: 1-2: 60x mode 2-3: MPX mode                                                                                        |

| JP6<br>(I <sup>2</sup> C_WP)                         | Out                                                                                | I <sup>2</sup> C memory is not write protected. | When this jumper is In, the I <sup>2</sup> C memory on the CPU module is write protected.                                                                 |

Table 2: DB-MPC7455DDR-L3-S7 Module Resistors and DPRs

| Resistor                            | Shipping Configuration            | Assignment                 | Description                                                                                                                                                                                                                          |

|-------------------------------------|-----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPR4                                | 1-2                               | Single MV64360             | Selects multi-controller configuration:<br>1-2: Single-MV<br>2-3: Multi-MV                                                                                                                                                           |

| DPR3                                | 1-2                               | CPU bus voltage (2.5V)     | Selects the CPU bus voltage configuration:<br>1-2: 2.5V<br>2-3: 1.8V                                                                                                                                                                 |

| R109, R106,<br>R114, R113,<br>R112  | NOTE: Depends on the CPU's model. | CPU core voltage           | Selects the CPU core voltage supply: 1.3V: Out, Out, Out, Out, In 1.6V: Out, In, In, Out, In 1.8V: Out, In, Out, In, In 1.9V: Out, Out, In, In, In NOTE: The configuration must be according to the datasheet of the CPU being used. |

| R110, R104,<br>R56, R29,<br>R51,R45 | NOTE: Depends on the CPU's model. | CPU core voltage.          | Selects CPU core low voltage supply (currently not used): 1.9V: In, Out, In, In, In 1.8V: In, In, Out, In, In 1.6V: In, In, In, Out, In, In 1.3V: In, Out, Out, Out, In, In                                                          |

| DPR2,<br>DPR7                       | 1-2, 1-2                          | No PAL present             |                                                                                                                                                                                                                                      |

| R32,<br>R121,R55,<br>R34, R35       | Out, Out, Out, Out                | JTAG chain con-<br>nection | When inserted, the JTAG mechanism is available.                                                                                                                                                                                      |

| DPR6                                | 1-2                               | COP_TRST pulled up         | Selects if the COP_TRST is pulled high or low. 1-2: Pulled high 2-3: Pulled low.                                                                                                                                                     |

| DPR1                                | 1-2                               | BMODE0 =<br>HRESET         | Selects if BMODE0 is connected to GND or HRESET. See Motorola's MPC7455 user manual for more details.                                                                                                                                |

# Section 3. DB-SR71010-S7

### 3.1 Overview

The DB-SR71010-S7 is a CPU and L3 cache module. This module enables Marvell devices to operate with Sand-Craft's SR71010 CPU. The module plugs into the Socket-7 connector designed for it.

The DB-SR71010-S7 includes the following features:

- Up to 133 MHz CPU bus frequency

- CPU (SandCraft's SR71010 CPU)

- Onboard L3 cache (Supports 2 MB or 4 MB of L3 cache)

- Configurable jumpers for logic reset, I<sup>2</sup>C write protect and Vcc I/O voltage

- Configurable DPR for logic reset, L3 cache SRAM size

- · Configurable resistor for Linear or Interleave Burst mode, Vcc INT voltage

- Reference power supply circuit (supports various CPU voltages)

### 3.2 Description

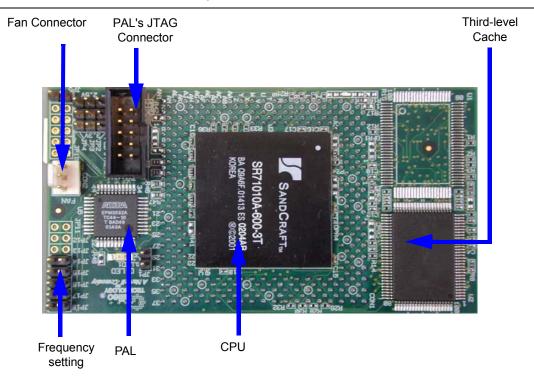

The DB-SR71010-S7 module components are illustrated in Figure 2.

Figure 2: DB-SR71010-S7 Module Components

# 3.3 DB-SR71010-S7 Module Jumpers

Table 3 details the DB-SR71010-S7 module jumpers.

Table 3: DB-SR71010-S7 Module Jumpers

| Jumper              | Shipping Configuration                 | Assignment                               | Description                                                                                                                                                                                              |

|---------------------|----------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1                 | In                                     | Write protect                            | Serial EEPROM Write protect:<br>In - Write protect<br>Out - Write enable                                                                                                                                 |

| JP2-JP4             | 1-2                                    | Configure Vcc I/O                        | Configure Vcc I/O to 2.5V/3.3V:<br>1-2: Vcc I/O 2.5V<br>2-3: Vcc I/O 3.3V                                                                                                                                |

| JP5                 | Out                                    |                                          | Reserved input to PAL                                                                                                                                                                                    |

| JP14<br>(Multi-4)   | Depends on the CPU's maximum frequency | CPU's bus frequency multiplied by 4      | The CPU's bus frequency multiplied by 4. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information.      |

| JP15<br>(Multi-4.5) | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 4.5 | The CPU internal frequency multiplied by 4.5. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

| JP16<br>(Multi-5)   | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 5   | The CPU internal frequency multiplied by 5. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information.   |

| JP17<br>(Multi-5.5) | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 5.5 | The CPU internal frequency multiplied by 5.5. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

| JP18<br>(Multi-6)   | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 6   | The CPU internal frequency multiplied by 6. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information.   |

Table 4 details the DB-SR71010-S7 module resistor configuration.

Table 4: DB-SR71010-S7 Module Configuration Resistor

| Resistor | Shipping Configuration | Assignment       | Description                                                                                      |

|----------|------------------------|------------------|--------------------------------------------------------------------------------------------------|

| R6       | Not connected          | Interleave Burst | Linear or Interleave Burst mode:<br>Connected - Linear Burst<br>Not connected - Interleave Burst |

### Section 4. DB-IBM750CXe-S7

### 4.1 Overview

The DB-IBM750CXe-S7 is a CPU module that enables Marvell devices to operate with IBM's 750CXe CPU. The module plugs into the Socket-7 connector designed for it.

The DB-IBM750CXe-S7 includes the following features:

- Up to 133 MHz CPU bus frequency

- 60x bus arbiter (supports Marvell's internal 60x bus arbiter, or any other arbiter placed on the backplane)

- Debug interface (COP interface, standard 16-bit header)

- Reference power supply circuit (supports various CPU voltages)

### 4.2 Description

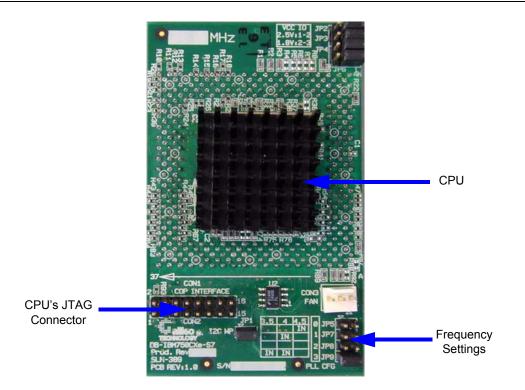

The DB-IBM750CXe-S7 module components are illustrated in Figure 3.

Figure 3: DB-IBM750CXe-S7 Module Components

# 4.3 DB-IBM750CXe-S7 Module Jumpers

Table 5 details the DB-IBM750CXe-S7 module jumpers.

Table 5: DB-IBM750CXe-S7 Module Jumpers

| Jumper                            | Shipping Configuration | Assignment                                   | Descrip                         | tion         |                |                     |                             |

|-----------------------------------|------------------------|----------------------------------------------|---------------------------------|--------------|----------------|---------------------|-----------------------------|

| JP2, JP3,<br>JP4, JP6<br>(Vcc IO) | 1-2, 1-2<br>1-2, 1-2   | CPU's Vcc I/O = 2.5V                         | the modi<br>same po<br>1-2: Vcc | ule. All fou | r jumpers<br>, |                     | s supplied to<br>set to the |

| JP5, JP7,                         | Depends on the CPU's   |                                              |                                 | JP 5         | JP7            | JP8                 | JP9                         |

| JP8, JP9<br>(PLL_CF)              | maximum frequency      |                                              | x3.5                            | Out          | Out            | Out                 | In                          |

|                                   |                        |                                              | х4                              | Out          | In             | Out                 | In                          |

|                                   |                        |                                              | x4.5                            | In           | Out            | Out                 | Out                         |

| JP1<br>(I <sup>2</sup> C_WP)      | Out                    | I <sup>2</sup> C memory not write protected. | When th                         |              | s In, the I    | <sup>2</sup> C memo | ory is write                |

Table 6: DB-IBM750CXe-S7 Module Resistors and DPRs

| Resistor                      | Shipping Configuration  | Assignment         | Description                                                                                                                                                                     |

|-------------------------------|-------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPR5                          | 1-2                     | Single MV64360     | Selects multi-controller configuration: 1-2: Single controller 2-3: Multi-controller                                                                                            |

| DPR2                          | 1-2                     | CPU bus voltage    | Selects CPU bus voltage configuration:<br>1-2: 2.5V<br>2-3: 1.8V                                                                                                                |

| R88, R87,<br>R92, R91,<br>R90 | Depends on CPU's model. |                    | Selects CPU core voltage supply: 1.65V: In, In, In, Out, in 1.80V: Out, In, Out, In, in 1.90V: Out, Out, In, In, in                                                             |

| R85, R89,<br>R8, R33,<br>R29  | Depends on CPU's model. | CPU core voltage   | Selects CPU Core Low Voltage Supply (currently not used): 1.9V: In, Out, In, In, In, In 1.8V: In, In, Out, In, In, In 1.6V: In, In, Out, In, In 1.3V: In, Out, Out, Out, In, In |

| DPR3,<br>DPR4                 | 1-2, 1-2                | No PAL present     |                                                                                                                                                                                 |

| R4, R5, R6,<br>R7,<br>R38     | Out, Out, Out, Out      | No JTAG connection | When resistors inserted, the JTAG mechanism is available                                                                                                                        |

### Table 6: DB-IBM750CXe-S7 Module Resistors and DPRs (Continued)

| Resistor | Shipping Configuration | Assignment         | Description                                |

|----------|------------------------|--------------------|--------------------------------------------|

| DPR1     | 1-2                    | COP_TRST pulled up | Selects if COP_TRST is pulled high or low. |

### Section 5. DB-IBM750FX-S7

### 5.1 Overview

The DB-IBM750FX-S7 is a CPU module compatible with the Socket-7 mechanism. It provides the interface between the CPU and main board, enabling the Marvell device to operate with IBM's 750FX CPU.

The DB-IBM750FX-S7 includes the following features:

- Up to 133 MHz CPU bus frequency.

- 60x bus arbiter (Supports Marvell's internal 60x bus arbiter, or any other arbiter placed on the backplane.)

- Debug interface (COP interface (standard 16-bit header)

- Reference power supply circuit (supports various CPU voltages)

### 5.2 Description

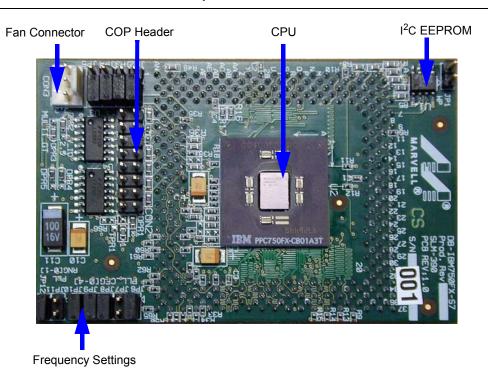

The DB-IBM750FX-S7 module components are illustrated in Figure 4.

Figure 4: DB-IBM750FX-S7 Module Components

Doc. No. MV-L100047-10, Rev. E

# 5.3 DB-IBM750FX-S7 Module Jumpers

Table 7 details the DB-IBM750FX-S7 module jumpers.

Table 7: DB-IBM750FX-S7 Module Jumpers

| Jumper                                     | Shipping Configuration | Assignment                                        | Description                                                                                                                                                                                                                                                 |  |

|--------------------------------------------|------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| JP2, JP3,<br>JP4, JP5<br>(Vcc IO)          | 2-3, 2-3<br>2-3, 2-3   | CPU's Vcc I/O =                                   | These jumpers select the Vcc I/O that is supplied to the module. All four jumpers must be set to the same position (either all left or all right).  1-2: Vcc I/O = 1.8V  2-3: Vcc I/O = 2.5V                                                                |  |

| JP6, JP7,<br>JP8, JP9,<br>JP10<br>(PLL_CF) | System dependent       |                                                   | The CPU's PLL configuration for the internal frequency multiplication. The following details the most common configuration assuming the system's clock (sysclock) is 133 MHz.  Frequency JP6 JP7 JP8 JP9 JP10 (MHz)  533 In Out In In In  600 In Out In Out |  |

| JP11, JP12                                 | System dependent       |                                                   | The CPU's PLL range configuration for internal frequency range:  Frequency JP11 JP12 (MHz) 500-750 In In                                                                                                                                                    |  |

| JP1<br>(I <sup>2</sup> C_WP)               | Out                    | I <sup>2</sup> C EEPROM's write protect disabled. | This jumper controls the I <sup>2</sup> C EEPROM write protect mode. Inserting this jumper sets the I <sup>2</sup> C EEPROM's write protect mode to enable, thus the EEPROM cannot be written.                                                              |  |

Table 8: DB-IBM750FX-S7 Module Resistors and DPRs

| Resistor      | Shipping Configuration | Assignment      | Description                                                                                                                            |

|---------------|------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| DPR3          | 1-2                    | Single MV64360  | This DPR selects between multi or single controller: 1-2: Single controller 2-3: Multi-controller                                      |

| DPR1,<br>TPR1 | 1-2, 1-2               | CPU bus voltage | Selects CPU bus voltage configuration:<br>1.2, 1.5 or 1.8V: DPR1 2-3, TPR1 1-2<br>2.5V: DPR1 1-2, TPR1 1-2<br>3.3V: DPR1 1-2, TPR1 2-4 |

### Table 8: DB-IBM750FX-S7 Module Resistors and DPRs (Continued)

| Resistor                      | Shipping Configuration | Assignment         | Description                                                                                                            |

|-------------------------------|------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|

| R1, R8, R2,<br>R4, R3         | System dependant       | CPU core voltage   | Selects CPU core voltage supply (VccInt): 1.2V: Out, Out, Out, Out 1.3V: Out, Out, Out, In 1.4V: Out, In, Out, Out, In |

| R55, R37,<br>R36, R54,<br>R35 | Out, Out, Out, Out     | No JTAG connection | When resistors inserted, the JTAG mechanism is available                                                               |

# Section 6. DB-RM7000A/B-S7 Module

The DB-RM7000A/B-S7 is a CPU and L3 cache module. This module enables Marvell devices to operate with QED's RM7000A/B CPUs. The module plugs into the Socket-7 connector designed for it.

The DB-RM7000A/B-S7 includes the following features:

- Up to 125 MHz CPU bus frequency

- Onboard L3 cache which supports 2 MB or 4 MB of L3 cache

- Configurable jumpers for logic reset

- Configurable DPR for logic reset, L3 cache (SRAM size), L3 cache (TAG RAM type), backplane indication

- · Configurable resistor for Linear or Interleave Burst mode, VCC INT voltage

- Reference power supply circuit which supports a number of CPU voltages

### 6.1 Description

The DB-RM7000A/B-S7 module components are illustrated in Figure 5.

Figure 5: DB-RM7000A/B-S7 Module Components

# 6.2 DB-RM7000A/B-S7 Module Jumpers

Table 9 details the DB-RM7000A/B-S7 module jumpers.

Table 9: DB-RM7000A/B-S7 Module Jumpers

| Jumper                    | Shipping Configuration                 | Assignment                               | Description                                                                                                                                                                                                                            |

|---------------------------|----------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1                       | In                                     | Write protect                            | Serial EEPROM Write protect: In: Write protect Out: Write enable                                                                                                                                                                       |

| JP2-JP4                   | 1-2                                    | Configure Vcc IO                         | Configure Vcc IO to 2.5V/3.3V:<br>1-2: Vcc IO 2.5V<br>2-3: Vcc IO 3.3V                                                                                                                                                                 |

| JP5                       | Out                                    |                                          | Reserved input to PAL                                                                                                                                                                                                                  |

| JP6<br>(CFG11)            | In                                     | CPU timer interrupt disable              | Disables timer interrupt on INT[5]: (For VxWorks, must be "In".) In: Timer interrupt enable Out: Timer interrupt disable                                                                                                               |

| JP7<br>(CFG12)            | Out                                    | Enable tertiary cache                    | Tertiary cache interface:<br>In: Disable<br>Out: Enable                                                                                                                                                                                |

| JP8<br>(CFG25)            | Out                                    | Enable secondary cache                   | Enables integrated secondary cache:<br>In: Disable<br>Out: Enable                                                                                                                                                                      |

| JP9<br>(CFG26)            | Out                                    | Disable                                  | Enables two outstanding read write out- of-order returns: In: Enable Out: Disable NOTE: This feature can only be enabled if the tertiary cache is disabled.                                                                            |

| JP10<br>(DRVOUT-<br>FAST) | Out                                    | CPU output drive slow rate control       | CPU output drive slow rate control:<br>In: 100%<br>Out: 83%                                                                                                                                                                            |

| JP11<br>(Multi- 2.5)      | Depends on the CPU's maximum frequency | CPU's bus frequency<br>multiplied by 2.5 | The CPU's bus frequency multiplied by 2.5. If more than one jumper is used, the lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

| JP12<br>(Multi-3)         | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 3   | The CPU internal frequency multiplied by 3. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information.                                 |

Table 9: DB-RM7000A/B-S7 Module Jumpers (Continued)

| Jumper              | Shipping Configuration                 | Assignment                                  | Description                                                                                                                                                                                              |

|---------------------|----------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP13<br>(Multi-3.5) | Depends on the CPU's maximum frequency | CPU internal frequency<br>multiplied by 3.5 | The CPU internal frequency multiplied by 3.5. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

| JP14<br>(Multi-4)   | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 4      | The CPU internal frequency multiplied by 4. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information.   |

| JP15<br>(Multi-4.5) | Depends on the CPU's maximum frequency | CPU internal frequency<br>multiplied by 4.5 | The CPU internal frequency multiplied by 4.5. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

| JP16<br>(Multi-5)   | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 5      | The CPU internal frequency multiplied by 5. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information.   |

| JP17<br>(Multi-5.5) | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 5.5    | The CPU internal frequency multiplied by 5.5. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

| JP18<br>(Multi-6)   | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 6      | The CPU internal frequency multiplied by 6. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information.   |

Table 10 details the DB-RM7000A/B-S7 module DPRs.

Table 10: DB-RM7000A/B-S7 Module DPRs

| DPR   | Shipping Configuration | Assignment             | Description                                                                                       |

|-------|------------------------|------------------------|---------------------------------------------------------------------------------------------------|

| DPR1  | 1-2                    | 2 MB Third-level cache | Configuration for 2 MB or 4 MB Third-level cache: 1-2: 2 MB 2-3: 4 MB                             |

| DPR2  | 1-2                    | 2 MB Third-level cache | Configuration for 2 MB or 4 MB Third-level cache: 1-2: 2 MB 2-3: 4 MB                             |

| DPR3  | 1-2                    | GS84118T               | Configuration for GS84118T or MCM69T618/GVT164T18 tag RAM: 1-2: GS84118T 2-3: MCM69T618/GVT164T18 |

| DPR4  | 1-2                    | GS84118T               | Configuration for GS84118T or MCM69T618/GVT164T18 tag RAM: 1-2: GS84118T 2-3: MCM69T618/GVT164T18 |

| DPR5  | 1-2                    |                        | Reserved input to backplane PAL                                                                   |

| DPR6  | 1-2                    | 2 MB Third-level cache | Configuration for 2 MB or 4 MB Third-level cache: 1-2: 2 MB 2-3: 4 MB                             |

| DPR7  | 1-2                    | CPU type RM7000A/B     | Select CPU type RM7000A/B:<br>1-2: '0'<br>2-3: '1'                                                |

| DPR8  | 1-2                    | CPU type RM7000A/B     | Select CPU type:<br>1-2: '0'<br>2-3: '1'                                                          |

| DPR9  | 1-2                    | LVCMOS                 | CPU interface to GT is HSTL or LVC-MOS: 1-2: LVCMOS 2-3: HSTL                                     |

| DPR10 | 1-2                    | Vcc IO voltage 2.5V    | Indication of Vcc IO voltage for back-<br>plane 2.5V/3.3V:<br>1-2: 2.5V<br>2-3: 3.3V              |

| DPR11 | 1-2                    | Big Endian             | Specified byte ordering Big Endian or<br>Little Endian:<br>1-2: Big Endian<br>2-3: Little Endian  |

Table 11 details the RM7000A/B module resistor configuration.

Table 11: DB-RM7000A/B-S7 Module Configuration Resistor

| Resistor | Shipping Configuration | Assignment       | Description                                                                                      |

|----------|------------------------|------------------|--------------------------------------------------------------------------------------------------|

| R6       | Not connected          | Interleave Burst | Linear or Interleave Burst mode:<br>Connected - Linear Burst<br>Not connected - Interleave Burst |

Table 12 details the DB-RM7000A/B module Vcc INT voltage resistor configuration.

Table 12: Vcc INT Voltage Resistor Configuration

| Resistor | RM7000A - 1.65V Vcc INT | RM7000B - 1.5V Vcc INT |

|----------|-------------------------|------------------------|

| R15      | Connected               | Connected              |

| R16      | Connected               | Connected              |

| R17      | Not connected           | Not connected          |

| R19      | Connected               | Not connected          |

| R20      | Connected               | Not connected          |

| R21      | Not connected           | Not connected          |

| R22      | Not connected           | Not connected          |

| R41      | Not connected           | Not connected          |

| R42      | Not connected           | Not connected          |

| R43      | Not connected           | Not connected          |

| R48      | Not connected           | Not connected          |

# Section 7. DB-RM7000C

The DB-RM7000C is a CPU and L3 cache module. This module enables Marvell devices to operate with RM7000C CPUs. The module plugs into the Socket-7 connector designed for it.

The DB-RM7000C includes the following features:

- Up to 200 MHz maximum frequency using HSTL signaling on the SysAD bus

- Onboard L3 cache

- Supports EZ cache protocol, which eliminates the need for external tag RAMs

- Configurable jumpers for logic reset

- Configurable DPR for logic reset, backplane indication

- Configurable resistor for Linear or Interleave Burst mode, Vcc INT voltage

- Reference power supply circuit

- Supports a number of CPU voltages

### 7.1 Description

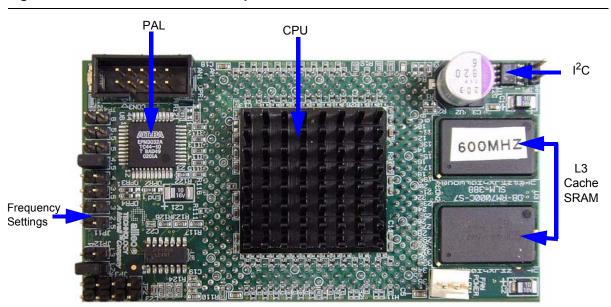

The DB-RM7000C module components are illustrated in Figure 6.

Figure 6: DB-RM7000C Module Components

# 7.2 DB-RM7000C Module Jumpers

Table 13 details the DB-RM7000C module jumpers.

Table 13: DB-RM7000C Module Jumpers

| Jumper   | Shipping Configuration | Assignment                                     | Description                                                                                                                                                 |

|----------|------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP15     | Out                    | Reserved input for PAL                         |                                                                                                                                                             |

| JP3      | In                     | TmrIntEn                                       | Timer Interrupt In: Enabled Out: Disabled                                                                                                                   |

| JP12     | Out                    | Tertiary cache interface                       | Enable tertiary cache In: Disabled Out: Enabled                                                                                                             |

| JP14     | Out                    | Integrated Secondary cache                     | Enable secondary cache In: Disabled Out: Enabled                                                                                                            |

| JP2      | Out                    | Two outstanding reads with out-of-order return | Enables two outstanding read write out- of-order returns: In: Enable Out: Disable NOTE: This feature can only be enabled if the tertiary cache is disabled. |

| JP4-JP11 | CPU Dependant          | CPU interface frequency multipliers            | The default value is x2 (all jumpers are Out.) If more than one jumper is, inserted, the smallest value is taken.                                           |

| JP13     | Out                    | CPU output drive slew rate control: 100/83%    | In: 100%<br>Out: 83%                                                                                                                                        |

| JP1      | Out                    | I <sup>2</sup> C write protect                 | In: Write protect Out: No write protect                                                                                                                     |

Table 14 details the DB-RM7000C module DPR.

Table 14: DB-RM7000C Module DPR

| DPR  | Shipping Configuration | Assignment                                                                  | Description                                                  |

|------|------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------|

| DPR1 | Connected on pins 1-2  | PAL[0]                                                                      | Reserved for internal use                                    |

| DPR2 | Connected on pins 1-2  | EndBlt - Specifies byte ordering. Logically ORed with the Big Endian signal | Big Endian Ordering<br>1-2: Big endian<br>2-3: Little Endian |

| DPR3 | Connected on pins 1-2  | CPU_TYPE0                                                                   | RM7000C                                                      |

| DPR4 | Connected on pins 1-2  | CPU_TYPE1                                                                   | RM7000C                                                      |

Table 14: DB-RM7000C Module DPR (Continued)

| DPR  | Shipping Configuration | Assignment | Description               |

|------|------------------------|------------|---------------------------|

| DPR5 | Connected on pins 1-2  | SRAM0 ZQ   | Reserved for internal use |

| DPR6 | Connected on pins 1-2  | SRAM1 ZQ   | Reserved for internal use |

Table 15 details the DB-RM7000C module Vcc INT voltage resistor configuration.

Table 15: Vcc INT Voltage Resistor Configuration

| Resistor | RM7000C - Vcc INT             |

|----------|-------------------------------|

| R1       | Depends on local CPU voltage. |

| R2       | Depends on local CPU voltage. |

| R3       | Depends on local CPU voltage. |

| R4       | Depends on local CPU voltage. |

| R5       | Depends on local CPU voltage. |

| R6       | Depends on local CPU voltage. |

| R7       | Depends on local CPU voltage. |

| R109     | Depends on local CPU voltage. |

| R112     | Depends on local CPU voltage. |

| R116     | Depends on local CPU voltage. |

January 30, 2003, Preliminary

# Section 8. DB-RM9000 Module

The DB-RM9000 is a CPU and L3 cache module. This module enables Marvell devices to operate with QED's RM9000 CPUs.

The DB-RM9000 includes the following features:

- Up to 125 MHz CPU bus frequency in CMOS mode, and 200 MHz in HSTL mode

- CPU RM9000

- Configurable jumpers for logic reset

- 128 DDR Memory (166 Mhz Max) connected to the CPU dedicated interface.

#### Note

The DB-RM9000 has a number of restrictions. For a list of restrictions, see "DB-RM9000 Restrictions" on page 30.

### 8.1 Description

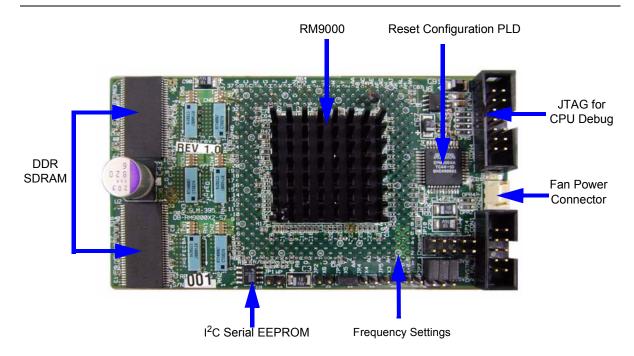

The DB-RM9000 module components are illustrated in Figure 7.

Figure 7: DB-RM9000 Module Components

January 30, 2003, Preliminary

# 8.2 DB-RM9000 Module Jumpers

Table 16 details the DB-RM9000 module jumpers.

Table 16: DB-RM9000 Module Jumpers

| Jumper  | Shipping Configuration                  | Assignment                                | Description                                                                                                                                                                                            |

|---------|-----------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1     | In                                      | Write protect                             | Serial EEPROM Write protect: In: Write protect Out: Write enable                                                                                                                                       |

| JP7-JP9 | 1-2                                     | Configure Vcc IO                          | Configure Vcc IO to 1.5V/3.3V:<br>1-2: Vcc IO 3.3V<br>2-3: Vcc IO 1.5V (HSTL mode)                                                                                                                     |

| JP11    | Out                                     | CPU Core B enable                         | In: Core B enable<br>Out: Core B disable                                                                                                                                                               |

| JP13    | In                                      | CPU timer interrupt disable               | Disables timer interrupt on INT[5] (For VxWorks, must be "In".) In: Timer interrupt enable Out: Timer interrupt disable                                                                                |

| JP14    | Out                                     | CPU output drive slew rate control (100%) | CPU output drive slew rate control:<br>In: 100%<br>Out: 83%                                                                                                                                            |

| JP10    | Out                                     | Not in use.                               |                                                                                                                                                                                                        |

| JP6     | Depends on the CPU's maximum frequency  |                                           | Add 0.5 to the CPU internal frequency multiplier (configured by JP7-JP9).                                                                                                                              |

| JP5     | Depends on the CPU's maximum frequency  | CPU internal frequency multiplied by 3.   | The CPU internal frequency multiplied by 3. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

| JP4     | Depends on the CPU's maximum frequency. | CPU internal frequency multiplied by 5.   | The CPU internal frequency multiplied by 5. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

| JP3     | Depends on the CPU's maximum frequency  | CPU internal frequency multiplied by 7.   | The CPU internal frequency multiplied by 7. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

Table 16: DB-RM9000 Module Jumpers (Continued)

| Jumper | Shipping Configuration                 | Assignment                              | Description                                                                                                                                                                                            |

|--------|----------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP2    | Depends on the CPU's maximum frequency | CPU internal frequency multiplied by 8. | The CPU internal frequency multiplied by 8. The lowest value is used. The maximum frequency is limited by the CPU device capabilities. Refer to the respective CPU specification for more information. |

| JP12   | Out                                    | Second level cache enable               | In: Disable<br>Out: Enable                                                                                                                                                                             |

Table 17 details the DB-RM9000 module DPR.

Table 17: DB-RM9000 Module DPR

| DPR   | Shipping Configuration | Assignment                     | Description                                                                                      |

|-------|------------------------|--------------------------------|--------------------------------------------------------------------------------------------------|

| DPR1  | 1-2                    |                                | Reserved input to PAL                                                                            |

| DPR10 | 1-2                    | LVCMOS                         | CPU interface to MV is HSTL or LVC-MOS: 1-2- LVCMOS 2-3- HSTL                                    |

| DPR3  | 2-3                    | Vcc IO voltage                 | Indication of Vcc IO voltage for back-<br>plane 1.5V/3.3V:<br>1-2: 1.5V<br>2-3: 3.3V             |

| DPR4  | 1-2                    | Big Endian                     | Specified byte ordering Big Endian or<br>Little Endian:<br>1-2- Big Endian<br>2-3- Little Endian |

| DPR5  | 1-2                    | SPARE0 (into the PAL)          | 1-2- "1"                                                                                         |

| DPR6  | 1-2                    | SPARE1 (into the PAL)          | 2-3- "0"                                                                                         |

| DPR7  | 1-2                    | 1-2: Pull-Down<br>2-3: Pull-Up | Reserved                                                                                         |

| DPR8  | 1-2                    | 1-2: Pull-Up<br>2-3: Pull-Down | Reserved.                                                                                        |

| DPR9  | 1-2                    | 1-2: Pull-Up<br>2-3: Pull-Down | Reserved.                                                                                        |

| DPR2  | 1-2                    | CPU bus voltage type           | 1-2: CMOS<br>2-3: HSTL                                                                           |

Table 18 details the DB-RM9000 module VCC INT voltage resistor configuration.

Table 18: VCC INT Voltage Resistor Configuration

| Resistor | DB-RM9000 - 1.25V Vcc INT |

|----------|---------------------------|

| R6       | Not connected             |

| R7       | Not connected             |

| R5       | Not connected             |

| R11      | Not connected             |

| R12      | Not connected             |

| R14      | Not connected             |

| R1       | Not connected             |

| R25      | Not connected             |

| R97      | Not connected             |

| R42      | Not connected             |

### 8.3 DB-RM9000 Restrictions

The DB-RM9000 has the followings restrictions:

- When using the DB-RM9000 with the DB-64340-BP and PMON monitor, the DB-64340-BP can only be equipped with 128 MB of memory. Using more than 128 MB will cause the system to hang.

- The RM9000 internal registers base address is set by the boot stream initialization PAL to address: 0x8000000. To use a different base address, reprogram the PAL. The source code for the PAL can be found on the secure web site.

# **Section 9. Revision History**

Table 19: Revision History

| Revision<br>Number | Date             | Comments                                                                                                                                                                                                                                                                |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. A             | May 21, 2002     | First Release                                                                                                                                                                                                                                                           |

| Rev. B             | June 12, 2002    | <ol> <li>Added Section 3 (DB-SR71010-S7)</li> <li>Added Section 4 (DB-IBM750CXe-S7)</li> <li>Added Section 5 (DB-IBM750FX-S7)</li> <li>Added Section 6 (DB-MPC7410-S7)</li> </ol>                                                                                       |

| Rev. C.            | June 19, 2002    | <ol> <li>Updated Section 2 (DB-MPC7455DDR-L3-S7)</li> <li>Deleted Section 6 (DB-MPC7410-S7)</li> </ol>                                                                                                                                                                  |

| Rev. D             | Nov. 26, 2002    | <ol> <li>Updated the Jumper settings in Table 1 of Section 2.</li> <li>Changed JP2-JP4 shipping configuration in Table 3 of Section 3.</li> <li>Added Section 6 (DB-RM7000A/B-S7)</li> <li>Added Section 7 (DB-RM7000C)</li> <li>Added Section 8 (DB-RM9000)</li> </ol> |

| Rev. E             | January 30, 2003 | <ol> <li>Updated Section 2 (DB-MPC7455DDR-L3-S7); note concerning<br/>L3 cache frequency added.</li> <li>Added Address Page</li> <li>Cover Page replaced</li> </ol>                                                                                                     |

#### MOVING FORWARD

FASTER®

#### Marvell Semiconductor, Inc.

700 First Avenue Sunnyvale, CA 94089

Phone 408.222.2500 Fax 408.752.9028

www.marvell.com

#### **US Worldwide Offices**

#### Marvell Semiconductor, Inc.

700 First Avenue Sunnyvale, CA 94089 Tel: 1.408.222.2500

Fax: 1.408.752.9028

Marvell Asia Pte, Ltd.

151 Lorong Chuan, #02-05 New Tech Park Singapore 556741

Tel: 65.6756.1600 Fax: 65.6756.7600

Marvell Japan K.K.

Shinjuku Center Bldg. 50F 1-25-1, Nishi-Shinjuku, Shinjuku-ku

Tokyo 163-0650 Tel: 81.(0).3.5324.0355 Fax: 81.(0).3.5324.0354

#### Galileo Technology Ltd.

A Marvell Company

Moshav Manof D.N. Misgav 20184

Israel Tel: 972.4.99

Tel: 972.4.999.9555 Fax: 972.4.999.9574

### Worldwide Sales Offices

#### Western US Sales Office

#### Marvell

700 First Avenue Sunnyvale, CA 94089 Tel: 1.408.222.2500 Fax: 1.408.752.9028 Sales Fax: 1.408.752.9029

#### Central US Sales Office

#### Marvell

11709 Boulder Lane, Ste. #220 Austin, TX 78726 Tel: 1.512.336.1551 Fax: 1.512.336.1552

#### Eastern US/Canada Sales Office

#### Marvell

Knox Trail Office Bldg. 2352 Main Street Concord, MA 01742 Tel: 1.978.461.0563 Tel: 1.978.461.1406 Fax: 1.978.461.1405

#### **Europe Sales Office**

#### Marvell

3 Clifton Court Corner Hall Hemel Hempstead Hertfordshire, HP3 9XY United Kingdom Tel: 44.(0).1442.211668 Fax: 44.(0).1442.211543

#### Marvell

Fagerstagatan 4 163 08 Spanga Stockholm, Sweden Tel: 46.16.146348 Fax: 46.16.482425

#### Marvell

5 Rue Poincare 56400 Le Bono France Tel: 33.297.579697 Fax: 33.297.578933

#### Israel Sales Office

#### Marvell

Ofek Center Bldg. 2, Floor 2 Northern Industrial Zone LOD 71293 Israel Tel: 972.8.924.7555 Fax: 972.8.924.7554

#### China Sales Office

#### Marvell

5J, 1800 Zhong Shan West Road Shanghai, China 200233 Tel: 86.21.6440.1350 Fax: 86.21.6440.0799

#### Japan Sales Office

#### Marvell

Helios Kannai Bldg. 12F 3-21-2 Motohama-cho, Naka-ku Yokohama, Kanagawa Japan 231-0004 Tel: 81.45.222.8811 Fax: 81.45.222.8812

#### **Taiwan Sales Office**

### Marvell

12F-1, 128 Sec. 3 Ming Sheng East Road Taipei 105 Taiwan, R.O.C. Tel: 886.2.8712.5700 Fax: 886.2.8712.5707

For more information, visit our website at: www.marvell.com

© 2002 Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, the Galileo logo, and GalNet are registered trademarks of Marvell. Discovery, Fastwriter, Galileo Technology, GalTis, Horizon, Libertas and Prestera are trademarks of Marvell. All other trademarks are the property of their respective owners.