Doc. No. MV-L100051-10, Rev. D June 25, 2003

| Document Status          |                                                                                                                                                                                           |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advanced<br>Informatio   | This document contains design specifications for initial product development. Specifications may change without notice. Contact Marvell Field Application Engineers for more information. |  |  |

| Preliminar<br>Informatio |                                                                                                                                                                                           |  |  |

| Final<br>Informatio      | This document contains specifications on a product that is in final release. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.  |  |  |

| Revision (               | Code:                                                                                                                                                                                     |  |  |

| Preliminar               | ry Technical Publication:                                                                                                                                                                 |  |  |

|                          |                                                                                                                                                                                           |  |  |

| Docum                    | nent Conventions                                                                                                                                                                          |  |  |

|                          |                                                                                                                                                                                           |  |  |

| 7                        | Note                                                                                                                                                                                      |  |  |

| F                        | Provides related information or information of special importance.                                                                                                                        |  |  |

|                          | Caution                                                                                                                                                                                   |  |  |

| 1                        | Indicates potential damage to hardware or software, or loss of data.                                                                                                                      |  |  |

| 1/ m                     | Varning                                                                                                                                                                                   |  |  |

| Į į                      | ndicates a risk of personal injury.                                                                                                                                                       |  |  |

#### Preliminary Information

This document provides Preliminary information about the products described. All specifications described herein are based on design goals only. Do not use for final design. Visit the Marvell® web site at <a href="www.marvell.com">www.marvell.com</a> or call 1-866-674-7253 for the latest information on Marvell products.

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any particular purpose. Further, egard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell makes no commitment either to update or to keep current the information contained in this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications. The user should contact Marvell to obtain the latest specifications before finalizing a product design. Marvell assumes no responsibility, either for use of these products or for any infringements of patents and trademarks, or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Marvell. These products may include one or more optional functions. The user has the choice of implementing any particular optional functions. Should the user choose to implement any of these optional functions, it is possible that the use could be subject to third party intellectual property rights. Marvell recommends that the user investigate whether third party intellectual property rights are relevant to the intended use of these products and obtain licenses as appropriate under relevant intellectual property rights.

Marvell comprises Marvell Technology Group Ltd. (MTGL) and its subsidiaries, Marvell International Ltd. (MIL), Marvell Semiconductor, Inc. (MSI), Marvell Asia Pte Ltd. (MAPL), Marvell Japan K.K. (MJKK), Marvell Semiconductor Israel Ltd. (MSIL), and SysKonnect GmbH.

Export Controls. With respect to any of Marvell's Information, the user or recipient, in the absence of appropriate U.S. government authorization, agrees: 1) not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2; by not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are controlled for national security reasons by the EAR; and, 3) in the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to controls under the U.S. Munitions List ("USML"). At all times hereunder, the recipient of any such information.

Copyright © 2003. Marvell. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, and GalNet are registered trademarks of Marvell. Discovery, Fastwriter, GalTis, Horizon, Libertas, Link Street, NetGX, PHY Advantage, Prestera, Raising The Technology Bar, UniMAC, Virtual Cable Tester, and Yukon are trademarks of Marvell. All other trademarks are the property of their respective owners.

Marvell

700 First Avenue Sunnyvale, CA 94089 Phone: (408) 222 2500 Sales Fax: (408) 752 9029 Email commsales@marvell.com

Doc. No. MV-L100051-10 Rev. D

CONFIDENTIAL

Copyright © 2003 Marvell

Page 2

Document Classification: Proprietary Information

June 25, 2003, Preliminary

## **Table of Contents**

| SEC | CTION 1.   | Introduction                    | 5  |

|-----|------------|---------------------------------|----|

| 1.1 | DB-6434    | 0/60-BP Components and Features | 5  |

| 1.2 | Shipping   | g Contents                      | 6  |

| 1.3 | Related I  | Documentation                   | 6  |

| 1.4 | Addition   | al Collateral                   | 6  |

| SEC | CTION 2.   | DB-64340/60-BP DESCRIPTION      | 7  |

| SEC | CTION 3.   | GETTING STARTED                 | 9  |

| 3.1 | Addition   | al Required Items               | 9  |

| SEC | CTION 4.   | HARDWARE SETUP                  | 10 |

| 4.1 | DB-6434    | 0/60-BP Feature Settings        | 10 |

| 4.2 | Multi-Pu   | rpose Pins (MPPs)               | 18 |

| 4.3 | Indication | on and Warning LEDs             | 21 |

| 4.4 | PCI Auto   | -Detect                         | 22 |

| 4.5 | System I   | Memory (DIMM)                   | 22 |

| 4.6 | CPU Mod    | dule                            | 22 |

| 4.7 | Applying   | 9 Power to the DB-64340/60-BP   | 23 |

| SEC | CTION 5.   | Software                        | 24 |

| 5.1 | MV64340    | 0/360 Drivers                   | 24 |

| SEC | TION 6     | REVISION HISTORY                | 25 |

## **List of Tables**

| DB-64340/60-BP Components  DB-64340/60-BP Jumper Location |                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                           |                                                                                                                                                                                                                                                                                                                                                    |

| of Figures                                                |                                                                                                                                                                                                                                                                                                                                                    |

|                                                           |                                                                                                                                                                                                                                                                                                                                                    |

| Revision History                                          | 2                                                                                                                                                                                                                                                                                                                                                  |

| Indication and Warning LEDs                               | 2 <sup>-</sup>                                                                                                                                                                                                                                                                                                                                     |

| Connectors for a PC ATX-Case                              |                                                                                                                                                                                                                                                                                                                                                    |

| Multi-Purpose Pins                                        |                                                                                                                                                                                                                                                                                                                                                    |

|                                                           |                                                                                                                                                                                                                                                                                                                                                    |

| TWSI                                                      | 1 <sup>-</sup>                                                                                                                                                                                                                                                                                                                                     |

|                                                           |                                                                                                                                                                                                                                                                                                                                                    |

| ·                                                         |                                                                                                                                                                                                                                                                                                                                                    |

| ·                                                         |                                                                                                                                                                                                                                                                                                                                                    |

| •                                                         |                                                                                                                                                                                                                                                                                                                                                    |

|                                                           |                                                                                                                                                                                                                                                                                                                                                    |

|                                                           |                                                                                                                                                                                                                                                                                                                                                    |

| ITAG Chain Bynassing                                      | 10                                                                                                                                                                                                                                                                                                                                                 |

|                                                           | JTAG Chain Bypassing  Reset Sample  PCI Configuration  PCI Interrupts from PCI to MV-Interrupt Controller  PCI Interrupts from MV-PCI Interface to PCI0/PCI1  MPSC Devices and Boot Option Jumpers  Internal Use  TWSI  Related CPU Configuration  Multi-Purpose Pins  Connectors for a PC ATX-Case  Indication and Warning LEDs  Revision History |

## **Section 1. Introduction**

The DB-64340/60-BP Development Board was designed to evaluate the Marvell® high-end MV64340/360 system controller. The DB-64340/60-BP Development Board provides you with a reference design platform to begin system development prior to hardware availability.

## 1.1 DB-64340/60-BP Components and Features

The features and components of the DB-64340/60-BP Development Board are as follows:

- PPC Single/Dual processor support (Via one/two SOCKET-7 connectors):

- Motorola MPC7410

- Motorola MPC7455

- Motorola MPC7450

- IBM 750FX

- IBM 750CXE

- MIPS processor support (via one SOCKET-7 connector)

- RM7000A/B

- SR71010

- RM9000

- RM7000C (HSTL interface)

- Marvell's DB-64340/60-BP (133 MHz) system controller

- Features Marvell's MIPS/PPC system controller (2 X 66 64-bit MHz PCI 2.2 or 2 X 133 MHz PCI-X).

- Double Data Rate (DDR) SDRAM (PC266) Memory support:

- Dual Inline Memory Module (DIMM) sockets to support PC266 compliant (64, 128, 256, 512, or 1 Gb device) modules. Up to 8 GB of memory, registered and non-registered modules.

- Two COM ports connectors:

- Can be driven by the device module's Dual UART or the MV64340/360's MPSCs.

- Two 60-pin MPSC connectors:

- Connected to the MV64340/360 MPSC's interface and uses Marvell's special modules.

- Two-Wire Serial Interface (TWSI) EEPROM and interface:

- The MV64340/360 can be initialized from an TWSI EEPROM. It also has full TWSI master and slave capabilities. The TWSI bus is connected to two DDR SDRAM DIMMs and to a connector which allows the connection of external devices.

- The board is designed with the ATX form factor standard.

CONFIDENTIAL

## 1.2 Shipping Contents

The DB-64340/60-BP package is shipped with the following components.

- One DB-64340/60-BP Development Board

- One/two CPU modules installed on the board.

#### Warning

Do not remove the CPU modules from the board. Doing so may cause damage to the board and/ or the modules. Marvell takes no responsibility for damage caused to the boards or the modules if you do not heed this warning.

- One/two power modules

- One device module (EV-DEVICES-D144)

- One DDR SDRAM DIMM

#### Note

The DIMM must be installed for proper operation.

If any of the above items are missing or damaged, contact your distributor or local Marvell FAE.

#### 1.3 Related Documentation

See the Marvell SOCKET-7 CPU Modules User Manual for additional information.

## 1.4 Additional Collateral

See the Marvell website, http://www.marvell.com for the following collateral:

- PLD equations

- Assembly map drawings

- Monitor Manuals

- Monitor Source Code

- Software Drivers

- BOM

- Block Diagram

- A list of modules that work with this board

- Gerber files

## Section 2. DB-64340/60-BP Description

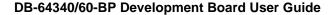

Figure 1 illustrates the main components on the board.

Figure 1: DB-64340/60-BP Components

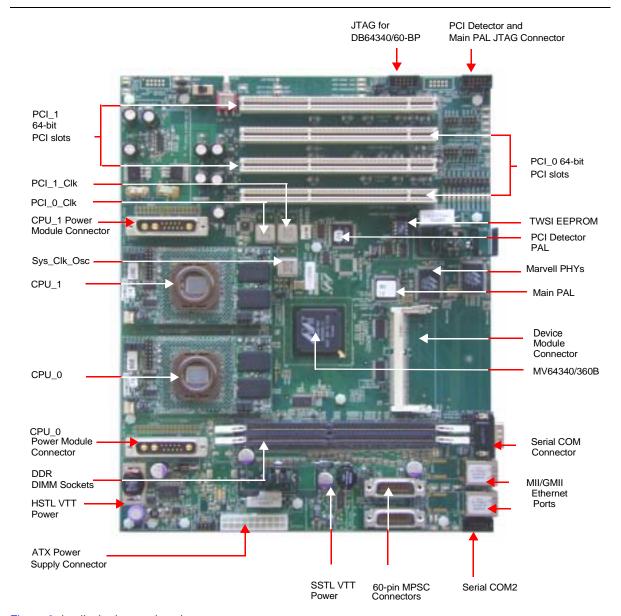

Figure 2 details the jumper locations.

Figure 2: DB-64340/60-BP Jumper Location

## Section 3. Getting Started

The DB-64340/60-BP is preconfigured and ready to run.

#### Note

Marvell recommends testing the board with this standard configuration before changing jumpers or other configuration options.

## 3.1 Additional Required Items

To use the DB-64340/60-BP Development Board, you need the following items which are not included in the board package:

- Null-modem cable, 9-pin (COM cable)

- ATX PC power supply

- Terminal emulation software, such as Windows 9x, or Windows NT HyperTerminal

## Section 4. Hardware Setup

The DB-64340/60-BP expansion cards contain delicate Integrated Circuits (ICs). To protect them against ESD damage, take the following precautions.

#### Warning

Make sure that the ATX power supply is switched off before you plug in or remove the ATX power connector on the DB-64340/60-BP.

- 1. Unplug the DB-64340/60-BP power supply.

- Use a grounded wrist strap before handling DB-64340/60-BP components. If you do not have one, touch your hands briefly to a safely grounded object or to a metal object, such as the power supply case, and then continue.

- 3. Hold the components by the edges and try not to touch the ICs, connectors, or other components.

- 4. Place components on a grounded anti-static pad or on the bag that came with the DB-64340/60-BP.

Take the following steps before applying power to the DB-64340/60-BP:

- 1. Check the DB-64340/60-BP settings. (See Section 4.1)

- 2. Install the memory modules. (See Section 4.5)

- 3. Install the CPU power module. (See Section 4.6)

- 4. Apply power to the DB-64340/60-BP. (See Section 4.7)

## 4.1 DB-64340/60-BP Feature Settings

The DB-64340/60-BP features are adjusted via the jumpers or the DPRs. The DPRs are used for various functions and are usually left in their default states.

DPRs are the same as 3-pad jumpers. The resistor can be placed on pads 1-2 or pads 2-3.

Table 1: JTAG Chain Bypassing

| JP/DPR         | Default      | Functionality                                                               |

|----------------|--------------|-----------------------------------------------------------------------------|

| DPR13<br>DPR14 | 1-2 (Bypass) | PHY1 JTAG Chain Bypass<br>1-2: Bypass<br>2-3: PHY1 in the chain.            |

| DPR15<br>DPR16 | 1-2 (Bypass) | PHY0 JTAG Chain Bypass<br>1-2: Bypass<br>2-3: PHY0 in the chain             |

| DPR1<br>DPR2   | 1-2 (Bypass) | PCI_1 Device8 JTAG Chain Bypass 1-2: Bypass 2-3: PCI_1 Device8 in the chain |

Table 1: JTAG Chain Bypassing (Continued)

| JP/DPR         | Default      | Functionality                                                               |

|----------------|--------------|-----------------------------------------------------------------------------|

| DPR3<br>DPR4   | 1-2 (Bypass) | PCI_0 Device8 JTAG Chain Bypass 1-2: Bypass 2-3: PCI_0 Device8 in the chain |

| DPR5<br>DPR6   | 1-2 (Bypass) | PCI_1 Device7 JTAG Chain Bypass 1-2: Bypass 2-3: PCI_1 Device7 in the chain |

| DPR7<br>DPR8   | 1-2 (Bypass) | PCI_0 Device7 JTAG Chain Bypass 1-2: Bypass 2-3: PCI_0 Device7 in the chain |

| DPR12<br>DPR17 | 1-2 (Bypass) | CPU_1 JTAG Chain Bypass 1-2: Bypass 2-3: CPU_1 in the chain                 |

| DPR22<br>DPR23 | 1-2 (Bypass) | CPU_0 JTAG Chain Bypass 1-2: Bypass 2-3: CPU_0 in the chain                 |

Table 2: Reset Sample

| DPR                        | Default            | Functionality                                                                                                                                                               |

|----------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPR51                      | 1-2 (Enable)       | DRAM Pad Calibration Enable 1-2: Enable 2-3: Disable                                                                                                                        |

| DPR47 [LSB]<br>DPR46 [MSB] | 1-2<br>1-2<br>'00' | Serial ROM Address '00': Address = 1010000 '01': Address = 1010001 '10': Address = 1010010 '11': Address = 1010011                                                          |

| DPR43                      | 1-2                | Internal Register Base Address<br>1-2: 0x14000000<br>2-3: 0xF1000000                                                                                                        |

| DPR42                      | 1-2 (Enable)       | CPU Pad Calibration Enable 1-2: Enable 2-3: Disable                                                                                                                         |

| DPR40 [LSB]<br>DPR39 [MSB] | 1-2<br>1-2<br>'00' | Multi-MV Address ID '00': MV response to CPU Address '00' '01': MV response to CPU Address '01' '10': MV response to CPU Address '10' '11': MV response to CPU Address '11' |

| DPR48                      | 1-2 (Enable)       | PCI_0 Pad Calibration Enable 1-2: Enable 2-3: Disable                                                                                                                       |

Table 2: Reset Sample (Continued)

| DPR                                             | Default                                       | Functionality                                                                                  |

|-------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------|

| DPR45                                           | 1-2 (Enable)                                  | PCI_1 Pad Calibration Enable 1-2: Enable 2-3: Disable                                          |

| DPR19                                           | 1-2 (Disable)                                 | PCI Retry<br>1-2: Disable<br>2-3: Enable                                                       |

| DPR49                                           | 1-2                                           | DRAM Clock 1-2: Core clock (Synchronized Clock) 2-3: Separate Clock (Asynch mode)              |

| DPR30                                           | 1-2 (pos-edge)                                | DRAM Address/Control toggle 1-2: pos-edge 2-3: neg-edge                                        |

| DPR33<br>DPR27                                  | 1-2<br>1-2<br>(One Stage)                     | DRAM Control pipeline [1:0] '00': Reserved '01': One Stage '10': Two stages '11': Three stages |

| DPR29<br>DPR35<br>DPR28                         | 1-2<br>1-2<br>1-2<br>'000'                    | DRAM read path control                                                                         |

| DPR26                                           | 1-2 (Disable)                                 | Giga Port #3 Enable<br>1-2: Disable<br>2-3: Enable                                             |

| DPR38 DPR37 DPR25 DPR24 DPR53 DPR52 DPR32 DPR32 | 2-3<br>2-3<br>1-2<br>2-3<br>1-2<br>2-3<br>1-2 | PLL1 N divider Default Value: "00101011" (N=43)                                                |

| DPR57                                           | 1-2                                           | PLL NP input<br>Default setting '1'                                                            |

| DPR55                                           | 1-2                                           | PLL1 HIKVCO input<br>Default setting '0'                                                       |

| DPR56                                           | 1-2<br>(Normal Operation)                     | DRAM PLL Power-up<br>1-2: PLL Power-up<br>2-3: PLL Power-down                                  |

Table 2: Reset Sample (Continued)

| DPR                                                | Default                                | Functionality                                                                       |

|----------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------|

| DPR82                                              | 1-2                                    | Giga Port 0 interface<br>1-2: MII/GMII<br>2-3: PCS                                  |

| DPR76<br>DPR74<br>DPR10<br>DPR73<br>DPR70<br>DPR69 | 1-2<br>2-3<br>1-2<br>1-2<br>1-2<br>2-3 | PLL1 M divider Default Value: "100010" (M=34)                                       |

| DPR83                                              | 1-2                                    | Giga Port 1 interface<br>1-2: MII/GMII<br>2-3: PCS                                  |

| DPR71                                              | 1-2                                    | JTAG Pad Calibration Bypass<br>1-2: Normal Operation<br>2-3: Bypass Pad Calibration |

| DPR77                                              | 1-2                                    | Core PLL Bypass 1-2: Normal Operation 2-3: Bypass the core's PLL                    |

| DPR78<br>DPR72<br>DPR75                            | 2-3<br>1-2<br>2-3                      | Core PLL Control                                                                    |

Table 3: PCI Configuration

| JP/DPR | Default      | Functionality                                        |

|--------|--------------|------------------------------------------------------|

| JP1    | 1-2 (3.3V)   | PCI_0 Vi/o select<br>1-2: 3.3V<br>2-3: 5V            |

| JP2    | 2-3 (64-bit) | PCI_1 32/64-bit select<br>1-2: 32-bit<br>2-3: 64-bit |

| JP3    | 2-3 (64-bit) | PCI_0 32/64-bit select<br>1-2: 32-bit<br>2-3: 64-bit |

| JP4    | 1-2 (3.3V)   | PCI_1 Vi/o select<br>1-2: 3.3V<br>2-3: 5V            |

| JP5    | Out          | PCI Arbiter DEBUG IN In: '0' Out: '1'                |

Table 3: PCI Configuration (Continued)

| JP/DPR                                         | Default        | Functionality                                                                                                       |

|------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------|

| DPR9 DPR79 DPR80 DPR81 DPR84 DPR85 DPR86 DPR87 | 1-2 (Internal) | Internal/External PCI Arbiter 1-2: Internal 2-3: External                                                           |

| JP22                                           | Out            | PCI_0 Conventional 33 MHz manual select In: Select PCI_0 conventional 33 MHz Out: Disable PCI_0 conventional 33 MHz |

| JP23                                           | Out            | PCI_0 Conventional 66 MHz manual select In: Select PCI_0 conventional 66 MHz Out: Disable PCI_0 conventional 66 MHz |

| JP24                                           | Out            | PCI_0 66 MHz PCI-X manual select In: Select PCI_0 PCI-X 66 MHz Out: Disable PCI_0 PCI-X 66 MHz                      |

| JP25                                           | Out            | PCI_0 100 MHz PCI-X manual select In: Select PCI_0 PCI-X 100 MHz Out: Disable PCI_0 PCI-X 100 MHz                   |

| JP26                                           | Out            | PCI_0 133 MHz PCI-X manual select In: Select PCI_0 PCI-X 133 MHz Out: Disable PCI_0 PCI-X 133 MHz                   |

| JP27                                           | Out            | PCI_1 Conventional 33 MHz manual select In: Select PCI_1 conventional 33 MHz Out: Disable PCI_1 conventional 33 MHz |

| JP28                                           | Out            | PCI_1 Conventional 66 MHz manual select In: Select PCI_1 conventional 66 MHz Out: Disable PCI_1 conventional 66 MHz |

| JP29                                           | Out            | PCI_1 66 MHz PCI-X manual select In: Select PCI_1 PCI-X 66 MHz Out: Disable PCI_1 PCI-X 66 MHz                      |

| JP30                                           | Out            | PCI_1 100 MHz PCI-X manual select In: Select PCI_1 PCI-X 100 MHz Out: Disable PCI_1 PCI-X 100 MHz                   |

| JP31                                           | Out            | PCI_1 133 MHz PCI-X manual select In: Select PCI_1 PCI-X 133 MHz Out: Disable PCI_1 PCI-X 133 MHz                   |

#### **Notes**

- In group JP22-JP26, only one jumper can be inserted. When all jumpers are out, the auto-detect function configures the PCI\_0 bus according to the PCI specification.

- In group JP27-JP31, only one jumper can be inserted. When all jumpers are out, the auto-detect function configures the PCI\_1 bus according to the PCI specification.

Table 4: PCI Interrupts from PCI to MV-Interrupt Controller

| Jumper | Default | Functionality                                                                                                                                        |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP6    | Out     | PCI_0 INT_A to MV Interrupt Controller In: Connect INT_A to MV Out: Disconnects INT_A from MV                                                        |

| JP7    | Out     | PCI_0 INT_B to MV Interrupt Controller In: Connect INT_B to MV Out: Disconnects INT_B from MV                                                        |

| JP8    | Out     | PCI_0 INT_C to MV Interrupt Controller In: Connect INT_C to MV Out: Disconnects INT_C from MV NOTE: Only one (JP6 or JP8) can be inserted at a time. |

| JP9    | Out     | PCI_0 INT_D to MV Interrupt Controller In: Connect INT_D to MV Out: Disconnects INT_D from MV NOTE: Only one (JP7 or JP9) can be inserted at a time. |

| JP10   | Out     | PCI_1 INT_A to MV Interrupt Controller In: Connect INT_A to MV Out: Disconnects INT_A from MV                                                        |

| JP11   | Out     | PCI_1 INT_B to MV Interrupt Controller In: Connect INT_B to MV Out: Disconnects INT_B from MV                                                        |

| JP12   | Out     | PCI_1 INT_C to MV Interrupt Controller In: Connect INT_C to MV Out: Disconnects INT_C from MV NOTE: Only one (JP6 or JP8) can be inserted at a time. |

| JP13   | Out     | PCI_1 INT_D to MV Interrupt Controller In: Connect INT_D to MV Out: Disconnects INT_D from MV NOTE: Only one (JP7 or JP9) can be inserted at a time. |

Table 5: PCI Interrupts from MV-PCI Interface to PCI0/PCI1

| Jumper | Default | Functionality                                                                                    |

|--------|---------|--------------------------------------------------------------------------------------------------|

| JP14   | Out     | PCI_0 INT_A from MV to PCI_0 bus. In: Drives INT_A to PCI_0 bus. Out: Disconnects INT_A from MV. |

Table 5: PCI Interrupts from MV-PCI Interface to PCI0/PCI1 (Continued)

| Jumper | Default | Functionality                                                                                    |

|--------|---------|--------------------------------------------------------------------------------------------------|

| JP15   | Out     | PCI_0 INT_B from MV to PCI_0 bus. In: Drives INT_B to PCI_0 bus. Out: Disconnects INT_B from MV. |

| JP16   | Out     | PCI_0 INT_C from MV to PCI_0 bus. In: Drives INT_C to PCI_0 bus. Out: Disconnects INT_C from MV. |

| JP17   | Out     | PCI_0 INT_D from MV to PCI_0 bus. In: Drives INT_D to PCI_0 bus. Out: Disconnects INT_D from MV. |

| JP18   | Out     | PCI_1 INT_A from MV to PCI_1 bus. In: Drives INT_A to PCI_1 bus. Out: Disconnects INT_A from MV. |

| JP19   | Out     | PCI_1 INT_B from MV to PCI_1 bus. In: Drives INT_B to PCI_1 bus. Out: Disconnects INT_B from MV. |

| JP20   | Out     | PCI_1 INT_C from MV to PCI_1 bus. In: Drives INT_C to PCI_1 bus. Out: Disconnects INT_C from MV. |

| JP21   | Out     | PCI_1 INT_D from MV to PCI_1 bus. In: Drives INT_D to PCI_1 bus. Out: Disconnects INT_D from MV. |

#### Table 6: MPSC Devices and Boot Option Jumpers

| Jumper | Default | Functionality                                                                                                     |

|--------|---------|-------------------------------------------------------------------------------------------------------------------|

| JP42   | 1-2     | UART Over MPSC to Connector<br>1-2: RS232 9-pin<br>2-3: MPSC_0 Connector.                                         |

| JP43   | 1-2     | UART Source 1-2: From UART located on the device module. 2-3: From UART over MPSC.                                |

| JP39   | Out     | NOT Supported                                                                                                     |

| JP40   | Out     | NOT Supported                                                                                                     |

| JP41   | Out     | Swap Boot Flash In: Boot from 32-bit flash on the Device Module. Out: Boot from 8-bit flash on the Device Module. |

Table 7: Internal Use

| JP/DPR                           | Default                  | Functionality                                              |

|----------------------------------|--------------------------|------------------------------------------------------------|

| DPR34<br>DPR36<br>DPR65<br>DPR68 | 1-2<br>1-2<br>1-2<br>1-2 | Pad Calibration Voltage                                    |

| JP35                             | Out                      | General Purpose #1 input to PAL<br>In: '1'<br>Out: '0'     |

| JP36                             | Out                      | General Purpose #0 input to PAL<br>In: '1'<br>Out: '0'     |

| JP37                             | 1-2 (CPU_VCC_IO)         | Clock to CPU Voltage. 1-2: Depends on CPU_VCC_IO 2-3: 2.5V |

#### Table 8: TWSI

| JP/DPR                  | Default           | Functionality                                                                       |

|-------------------------|-------------------|-------------------------------------------------------------------------------------|

| JP32                    | 2-3 (normal)      | TWSI Write Protect 1-2: Write Protect 2-3: Normal Operation                         |

| JP38                    | 1-2 (Disable)     | TWSI Support 1-2: Disable. 2-3: Enable. (Only if using Single/Double MPC7450 CPUs). |

| DPR90<br>DPR89<br>DPR88 | 1-2<br>1-2<br>1-2 | TWSI Address                                                                        |

#### Table 9: Related CPU Configuration

| DPR                                                | Default               | Functionality                                                                             |

|----------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------|

| DPR41<br>DPR21<br>DPR50<br>DPR64<br>DPR20<br>DPR11 | 1-2 (Internal)        | Internal/External CPU Arbiter 1-2: Internal 2-3: External                                 |

| JP45                                               | MIPS: 2-3<br>PPC: 1-2 | MIPS: 1-2: Little Endian 2-3: Big Endian PPC: 1-2: Internal Arbiter 2-3: External Arbiter |

Table 9: **Related CPU Configuration (Continued)**

| DPR   | Default | Functionality                                         |

|-------|---------|-------------------------------------------------------|

| DPR65 | 2-3     | Multi MV Socket Selection 1-2: Socket#1 2-3: Socket#0 |

#### Table 10: Connectors for a PC ATX-Case

| Jumper | Default | Functionality                                                                         |

|--------|---------|---------------------------------------------------------------------------------------|

| JP46   | 1-2     | Power Up source 1-2: On/off swtich or JP48 (ATX switch button). 2-3: ATX push button. |

| JP44   | Out     | External ATX push button.                                                             |

| JP33   | Out     | External ATX reset.                                                                   |

| JP48   | Out     | External ATX switch button.                                                           |

| JP49   | Out     | External Flash Busy Indication                                                        |

| JP50   | Out     | External Speaker Connector                                                            |

#### 4.2 **Multi-Purpose Pins (MPPs)**

The DB-64340/60-BP has 32 MPPs. Table 11 details the default MPP configuration (in the default column) that is shipped with the DB-64340/60-BP and supported by the DINK32 monitor and the VxWorks Operating System. The other columns detail additional options for the MPPs. These options are for internal use only.

#### Warning

Changing the configuration of the MPPs in the software (via the MPP registers) or changing the hardware connection on the board (via the jumpers) may cause the board to stop functioning. See the comments column for more details.

Table 11: **Multi-Purpose Pins**

| MPP# | Default | Multiplexed<br>#1 | Multiplexed #2 | Multiplexed #3 | Comments |

|------|---------|-------------------|----------------|----------------|----------|

| MPP0 | TxD0    |                   |                |                |          |

| MPP1 | RxD0    |                   |                |                |          |

| MPP2 | RTS0    |                   |                |                |          |

| MPP3 | CTS0    |                   |                |                |          |

| MPP4 | CD0     |                   |                |                |          |

Doc. No. MV-L100051-10 Rev. D Copyright © 2003 Marvell CONFIDENTIAL

Table 11: Multi-Purpose Pins (Continued)

| MPP#  | Default                                                                                   | Multiplexed<br>#1   | Multiplexed #2 | Multiplexed #3 | Comments                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------|---------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPP5  | SCLK0                                                                                     |                     |                |                |                                                                                                                                                      |

| MPP6  | TSCLK0                                                                                    |                     |                |                |                                                                                                                                                      |

| MPP7  | GPIO[7] –<br>G0_Int<br>Interrupt from<br>PHY_0<br>DPR58 1-2                               | CTS1<br>DPR58 2-3   |                |                | When MPSC_1 is working with its full protocol (not only RXD and TXD), PCI_1 Device7 and both interrupts driven from the PHYs will not be functional. |

| MPP8  | GNT1[4] –<br>grant from<br>PCI internal<br>arbiter to<br>PCI_1 device<br>7.<br>DPR54 1-2  | CD1<br>DPR54 2-3    |                |                |                                                                                                                                                      |

| MPP9  | REQ1[4] –<br>request from<br>PCI_1 device<br>7 to PCI inter-<br>nal arbiter.<br>DPR63 1-2 | SCLK1<br>DPR63 2-3  |                |                |                                                                                                                                                      |

| MPP10 | GPIO[10] –<br>G1_Int<br>Interrupt from<br>PHY_1<br>DPR59 1-2                              | TSCLK1<br>DPR59 2-3 |                |                |                                                                                                                                                      |

| MPP11 | RXD1                                                                                      |                     |                |                |                                                                                                                                                      |

| MPP12 | TXD1                                                                                      |                     |                |                |                                                                                                                                                      |

| MPP13 | RTS1                                                                                      |                     |                |                |                                                                                                                                                      |

| MPP14 | GNT1[1]] –<br>grant from<br>PCI internal<br>arbiter to<br>PCI_1 device<br>8.              |                     |                |                | These MPPs are for PCI_1 Device8 internal Arbiter control. Changing the default setting will cause PCI_1 Device8 to be non-functional.               |

| MPP15 | REQ1[1]] – request from PCI_1 device 8 to PCI internal arbiter.                           |                     |                |                |                                                                                                                                                      |

Table 11: Multi-Purpose Pins (Continued)

| MPP#  | Default                                                                       | Multiplexed<br>#1                           | Multiplexed #2       | Multiplexed #3                              | Comments                                                                                                                                                       |

|-------|-------------------------------------------------------------------------------|---------------------------------------------|----------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPP16 | GNT0[0] ] –<br>grant from<br>PCI internal<br>arbiter to<br>PCI_0 device<br>7. |                                             |                      |                                             | These MPPs are for PCI_0 Device7 and Device8 internal Arbiter control. Changing the default setting will cause PCI_0 Device7 and Device8 to be non-functional. |

| MPP17 | REQ0[0] ] – request from PCI_0 device 7 to PCI internal arbiter.              |                                             |                      |                                             |                                                                                                                                                                |

| MPP18 | GNT0[1] ] –<br>grant from<br>PCI internal<br>arbiter to<br>PCI_0 device<br>8. |                                             |                      |                                             |                                                                                                                                                                |

| MPP19 | REQ0[1]] – request from PCI_0 device 8 to PCI internal arbiter.               |                                             |                      |                                             |                                                                                                                                                                |

| MPP20 | InitAck                                                                       |                                             |                      |                                             | Both default settings are essential for I <sup>2</sup> C Boot and must                                                                                         |

| MPP21 | BclkIn                                                                        |                                             |                      |                                             | not be changed.                                                                                                                                                |

| MPP22 | GPIO[22] –<br>RS232B<br>interrupt.<br>DPR61 1-2                               | DmrEQ3<br>DPR61 2-3                         |                      |                                             | These multiple options are used for System Validation (SV) tests. Check the main PAL equations for more details                                                |

| MPP23 | BclkOut<br>DPR62 1-2<br>DPR18 1-2                                             | TBEN<br>DPR62 1-2<br>DPR18 2-3<br>DPR60 1-2 | DMAAck3<br>DPR62 2-3 | EOT0<br>DPR62 1-2<br>DPR18 2-3<br>DPR60 2-3 | on these tests.                                                                                                                                                |

| MPP24 | WDNMI                                                                         |                                             |                      |                                             |                                                                                                                                                                |

| MPP25 | WDE                                                                           | TCTcnt0                                     |                      |                                             | These multiple options are used for System Validation (SV) tests. Check the main PAL equations for more details on these tests.                                |

| MPP26 | GPIO[26] –<br>TP21 optional<br>TP<br>DPR67 1-2                                | TCEn1 DPR67 2-3                             |                      |                                             |                                                                                                                                                                |

| MPP27 | GPIO[27] –<br>RS232A                                                          |                                             |                      |                                             |                                                                                                                                                                |

Table 11: Multi-Purpose Pins (Continued)

| MPP#  | Default                              | Multiplexed<br>#1 | Multiplexed #2 | Multiplexed #3 | Comments |

|-------|--------------------------------------|-------------------|----------------|----------------|----------|

| MPP28 | GPIO[28] –<br>PCI1 B,D<br>interrupts |                   |                |                |          |

| MPP29 | GPIO[29] –<br>PCI1 A,C<br>interrupts |                   |                |                |          |

| MPP30 | GPIO[30] –<br>PCI0 B,D<br>interrupts |                   |                |                |          |

| MPP31 | GPIO[31] –<br>PCI1 A,C<br>interrupts |                   |                |                |          |

## 4.3 Indication and Warning LEDs

Table 12 provides a list of LEDs, their functionality and when they are lit.

Table 12: Indication and Warning LEDs

| LED    | Functionality                 | Lit When                                                                                                                                         |

|--------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| LED 21 | HSTL Mode Indication          | CPU interface is configured to HSTL mode.                                                                                                        |

| LED 20 | Multi-MV Mode Indication      | MV64340/60A is configured to Multi-MV mode.                                                                                                      |

| LED 19 | MPX Bus Indication            | CPU interface is configured to MPX bus mode.                                                                                                     |

| LED 16 | PCI External Arbiter Disabled | Working with the enabled MV64340/60A PCI internal arbiter.                                                                                       |

| LED 22 | CPU's V I/O differential      | Working with dual CPUs and each CPU requires a different CPU VI/O.                                                                               |

| LED 23 | CPU's bus type differential   | Working with dual CPUs and each CPU is configured to a different bus type. For example, CPU0 is configured to 60x and CPU1 is configured to MPX. |

#### Warning

When either LED 22 or 23 is lit, turn the power off immediately.

#### **PCI** Auto-Detect 44

The DB-64340/60-BP supports the PCI auto-detect feature. This mechanism is implemented according to the PCI-X specification, Rev. 1.0, Chapter 6.2 and Appendix E (Detection of PCI-X Add-in and capability.)

Each PCI interface has five LEDs and five respective jumpers.

- PCI Conventional 33 MHz

- PCI Conventional 66 MHz

- PCI-X 66 MHz

- PCI-X 100 MHz

- PCI-X 133 MHz

When one of the jumpers is inserted, the mode is set manually. The Auto-Detect feature is enabled when all five jumpers are "out".

#### System Memory (DIMM) 4.5

The DB-64340/60-BP only uses DDR (Double Data Rate) Dual Inline Memory Modules (DIMMs). Two sockets are available for 2.5 V power level unbuffered or registered DDR-Synchronous Dynamic Random Access Memory DDR (SDRAM) of 64, 128, 256, 512, or 1024 Mb.

#### **Notes**

- Only use DDR-SDRAMs that are compatible with the current PC266 DDR-SDRAM specification.

- Do not mix registered DDR-SDRAMs with unbuffered ones.

- When using registered DDR-SDRAM, configure the MV64340/360 prior to the CPU access of the DDR-SDRAM.

- When using two memory modules, install the larger module in CON17.

## 4.6 CPU Module

The DB-64340/60-BP provides two SOCKET-7 connectors for two CPU modules which are installed on the board. There are two power module connectors which provide each socket with the CPU's internal voltage.

#### Warning

Do not remove the CPU modules from the board. Doing so may cause damage to the board and/ or the modules. Marvell takes no responsibility for damage caused to the boards or the modules if you do not heed this warning.

#### Note

When one or both sockets are populated with a CPU module, the power module must be connected. Do not power up the system unless the power module is connected.

Doc. No. MV-L100051-10 Rev. D CONFIDENTIAL Copyright © 2003 Marvell Page 22 June 25, 2003, Preliminary

## 4.7 Applying Power to the DB-64340/60-BP

The DB-64340/60-BP uses a hyperterminal for communication with the system. You need an RS232 cable and a PC which runs a hyperterminal application. Take the following steps to apply power to the board:

- Make sure that all power switches are off.

- 2. Connect the power supply cord connector to the ATX header on the board.

- 3. Connect the RS232 cable to the COM1 port on the DB-64340/60-BP and to the PC's COM port.

- 4. Open the hyperterminal window. You will see a File Menu on your PC screen.

- 5. From the File menu, select File|Properties.

- 6. In the Properties dialog box, click Configure, and confirm that the displayed parameters match the parameters in Figure 3.

- 7. Click OK.

- 8. From the File Menu, Choose File. Follow the instructions below.

- 9. The CPU fan can be connected to the system in one of the following two options:

- Connect the CPU fan to the ATX power supply connector.

- Connect the CPU fan to the on-board CPU fan connector.

Figure 3: COM1 Properties Dialog Box

10. Turn on the power. The operating system's logo appears in the Main window. The power LEDs on the DB-64340/60-BP turn on. If, for some reason, one of LEDs does not turn on immediately, turn the power off. When the unit powers up, LED0, LED1, and LED2 light up in order. This is an indication that the monitor was fired up properly. Afterwards, these LEDs turn off. The system is now ready for operation.

## Section 5. Software

The DB-64340/60-BP is shipped with DINK 32 Operating System (PPC)/PMON operating system (MIPS). PMON was originally released by Algorithmics. Marvell has ported the PMON Operating System software so that it complies with the DB-64340/60-BP. It has many useful commands as well as a simple flash file system. You can download software to the DB-64340/60-BP via the hyperterminal or by using one of the Ethernet ports in conjunction with various application provided by Marvell.

#### **Notes**

- The commands will be listed in the PMON manual in the near future.

- The VxWorks Board Support Package is shipped with the IBM CPUs.

## 5.1 MV64340/360 Drivers

To ease the process of software development, Marvell is in the process of developing low-level drivers for the DB-64340/60-BP. These will be available in the near future.

# **Section 6. Revision History**

Table 13: Revision History

| Document Type | Rev. # | Date          | Comments                                                                                                                                                                                                                                                                               |

|---------------|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| First Release | Rev. A | May 20, 2002  |                                                                                                                                                                                                                                                                                        |

|               | Rev. B | June 26, 2002 | <ol> <li>Updated photograph in Figure 1.</li> <li>Updated the following tables: Table 1,<br/>Table 2, Table 3, Table 6 and Tables 7-<br/>12.</li> <li>Added Section 4.3 and Section 4.4.</li> </ol>                                                                                    |

|               | Rev. C | July 15,2002  | Added the following warning in Section 1.2 and Section 4.6: "Do not remove the CPU modules from the board. Doing so may cause damage to the board and/or the modules. Marvell takes no responsibility for damage caused to the boards or the modules if you do not heed this warning." |

|               | Rev. D | June 25, 2003 | <ol> <li>Added an additional CPU fan connection option in Section 4.7 Step 9.</li> <li>Updated Disclaimer</li> <li>Replaced I<sup>2</sup>C with TWSI.</li> <li>Picture Replaced</li> </ol>                                                                                             |

#### MOVING FORWARD

FASTER®

#### Marvell Semiconductor, Inc.

700 First Avenue Sunnyvale, CA 94089

Phone 408.222.2500 Fax 408.752.9028

www.marvell.com

#### **US and Worldwide Offices**

#### Marvell Semiconductor, Inc.

700 First Avenue Sunnyvale, CA 94089 Tel: 1.408.222.2500 Fax: 1.408.752.9028

#### Marvell Asia Pte, Ltd.

151 Lorong Chuan, #02-05 New Tech Park Singapore 556741 Tel: 65.6756.1600 Fax: 65.6756.7600

#### Marvell Japan K.K.

Shinjuku Center Bldg. 50F 1-25-1, Nishi-Shinjuku, Shinjuku-ku Tokyo 163-0650

Tel: 81.(0).3.5324.0355 Fax: 81.(0).3.5324.0354

#### Marvell Semiconductor Israel, Ltd.

Moshay Manof D.N. Misgav 20184 Israel

Tel: 972.4.995.1000 Fax: 972.4.995.1001

#### **Worldwide Sales Offices**

#### Western US Sales Office

#### Marvell

700 First Avenue Sunnyvale, CA 94089 Tel: 1.408.222.2500 Fax: 1.408.752.9028 Sales Fax: 1.408.752.9029

#### Central US Sales Office

#### Marvell

11709 Boulder Lane, Ste. #220 Austin, TX 78726 Tel: 1.512.336.1551 Fax: 1.512.336.1552

#### Eastern US/Canada Sales Office

#### Marvell

Knox Trail Office Bldg. 2352 Main Street Concord, MA 01742 Tel: 1.978.461.0563 Tel: 1.978.461.1406 Fax: 1.978.461.1405

#### **Europe Sales Office**

#### Marvell

3 Clifton Court Corner Hall Hemel Hempstead Hertfordshire, HP3 9XY United Kingdom Tel: 44.(0).1442.211668 Fax: 44.(0).1442.211543

#### Marvell

Fagerstagatan 4 163 08 Spanga Stockholm, Sweden Tel: 46.16.146348 Fax: 46.16.482425

#### Marvell

5 Rue Poincare 56400 Le Bono France Tel: 33.297.579697 Fax: 33.297.578933

#### Israel Sales Office

#### Marvell

Ofek Center Bldg. 2, Floor 2 Northern Industrial Zone LOD 71293 Israel Tel: 972.8.914.1300 Fax: 972.8.914.1301

#### **China Sales Office**

#### Marvell

5J, 1800 Zhong Shan West Road Shanghai, China 200233 Tel: 86.21.6440.1350 Fax: 86.21.6440.0799

#### Japan Sales Office

#### Marvell

Helios Kannai Bldg. 12F 3-21-2 Motohama-cho, Naka-ku Yokohama, Kanagawa Japan 231-0004 Tel: 81.45.222.8811 Fax: 81.45.222.8812

#### **Taiwan Sales Office**

Marvell 2FI., No. 1, Alley 20, Lane 407 Ti-Ding Blvd., Nei Fu District Taipei, Taiwan 114, R. O. C Tel: (886-2),7720,5700 FAX: (886-2).7720.5707

For more information, visit our website at: www.marvell.com