Doc. No. MV-S300165-00, Rev. A May 21, 2002

| Document Status                        |                                                                                                                                                                                                                          |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advanced<br>Information                | This datasheet contains design specifications for initial product development. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.                               |  |  |

| Preliminary<br>Information             | This datasheet contains preliminary data, and a revision of this document will be published at a later date. Specifications may change without notice. Contact Marvell Field Application Engineers for more information. |  |  |

| Final<br>Information                   | This datasheet contains specifications on a product that is in final release. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.                                |  |  |

| Revision Code:                         |                                                                                                                                                                                                                          |  |  |

| Preliminary Technical Publication: 0.x |                                                                                                                                                                                                                          |  |  |

### Preliminary Information

This document provides Preliminary information about the products described. All specifications described herein are based on design goals only. Do not use for final design. Visit the Marvell® web site at <a href="https://www.marvell.com">www.marvell.com</a> or call 1-866-674-7253 for the latest information on Marvell products.

Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell makes no commitment either to update or to keep current the information contained in this document. Marvell makes no commitment either to update or to keep current the information contained in this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products are not designed for use in life-support equipment or applications. The user should contact Marvell to obtain the latest specifications before finalizing a product design. Marvell assumes no responsibility, either for use of these products or for any infringements of patents and trademarks, or other rights of third parties resulting from its use. No license is granted under any patents, patent rights, or trademarks of Marvell. These products may include one or more optional functions. The user has the choice of implementing any particular optional function. Should the user choose to implement any of these optional functions, it is possible that the use could be subject to third party intellectual property rights. Marvell recommends that the user investigate whether third party intellectual property rights are relevant to the intended use of these products and obtain licenses as appropriate under relevant intellectual property rights.

Marvell comprises Marvell Technology Group Ltd. (MTGL) and its subsidiaries, Marvell International Ltd. (MIL), Marvell Semiconductor, Inc. (MSI), Marvell Asia Pte Ltd. (MAPL), Marvell Japan K.K. (MJKK), and Galileo Technology Ltd. (GTL).

Copyright © 2002 Marvell. All rights reserved. Marvell, the M logo, Moving Forward Faster, Alaska, and GalNet are registered trademarks of Marvell. Galileo, Galileo Technology, GalTis, GalStack, GalRack, NetGX, Prestera, Discovery, Horizon, Libertas, Fastwriter, the Max logo, Communications Systems on Silicon, and Max bandwidth are trademarks of Marvell. All other trademarks are the property of their respective owners.

Marvell 700 First Avenue Sunnyvale, CA 94089 Phone: (408) 222 2500 Sales Fax: (408) 752 9029 Email: commsales@marvell.com

# **Table of Contents**

| TION 1.   | Introduction                                                                                                                                                                                      | 11                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Related [ | Documentation                                                                                                                                                                                     | 11                                                                                                                                                                                                                                                                                                                                                                                               |

| TION 2.   | GT-64260A OVERVIEW                                                                                                                                                                                | 12                                                                                                                                                                                                                                                                                                                                                                                               |

| TION 3.   | CPU INTERFACE FUNCTIONAL OVERVIEW                                                                                                                                                                 | 14                                                                                                                                                                                                                                                                                                                                                                                               |

| CPU Pind  | out Description                                                                                                                                                                                   | 14                                                                                                                                                                                                                                                                                                                                                                                               |

| 60x Bus   | Mode                                                                                                                                                                                              | 17                                                                                                                                                                                                                                                                                                                                                                                               |

| MPX Bus   | s Mode                                                                                                                                                                                            | 18                                                                                                                                                                                                                                                                                                                                                                                               |

| Cache Co  | oherency                                                                                                                                                                                          | 18                                                                                                                                                                                                                                                                                                                                                                                               |

| Specific  | CPUs Aspects                                                                                                                                                                                      | 21                                                                                                                                                                                                                                                                                                                                                                                               |

| Multi-GT  | or Multi-slave Modes                                                                                                                                                                              | 24                                                                                                                                                                                                                                                                                                                                                                                               |

| CPU Bus   | Multiple Masters                                                                                                                                                                                  | 26                                                                                                                                                                                                                                                                                                                                                                                               |

| PowerPC   | COP/JTG Interface                                                                                                                                                                                 | 31                                                                                                                                                                                                                                                                                                                                                                                               |

| TION 4.   | SDRAM INTERFACE FUNCTIONAL OVERVIEW                                                                                                                                                               | 33                                                                                                                                                                                                                                                                                                                                                                                               |

| Pinout D  | escription                                                                                                                                                                                        | 33                                                                                                                                                                                                                                                                                                                                                                                               |

| Memory    | Connection                                                                                                                                                                                        | 35                                                                                                                                                                                                                                                                                                                                                                                               |

| SDRAM A   | Address Control                                                                                                                                                                                   | 39                                                                                                                                                                                                                                                                                                                                                                                               |

| SDRAM I   | nitialization                                                                                                                                                                                     | 40                                                                                                                                                                                                                                                                                                                                                                                               |

| ECC Sup   | port                                                                                                                                                                                              | 40                                                                                                                                                                                                                                                                                                                                                                                               |

| Memory    | Banks and Pages                                                                                                                                                                                   | 42                                                                                                                                                                                                                                                                                                                                                                                               |

| TION 5.   | PCI Interface Functional Overview                                                                                                                                                                 | 46                                                                                                                                                                                                                                                                                                                                                                                               |

| P2P Capa  | ability                                                                                                                                                                                           | 46                                                                                                                                                                                                                                                                                                                                                                                               |

| PCI Arbit | ration                                                                                                                                                                                            | 48                                                                                                                                                                                                                                                                                                                                                                                               |

| Delayed   | Read                                                                                                                                                                                              | 49                                                                                                                                                                                                                                                                                                                                                                                               |

| 32-bit PC | CI System                                                                                                                                                                                         | 49                                                                                                                                                                                                                                                                                                                                                                                               |

| Cache Co  | oherency                                                                                                                                                                                          | 50                                                                                                                                                                                                                                                                                                                                                                                               |

| Message   | Signaled Interrupt (MSI)                                                                                                                                                                          | 50                                                                                                                                                                                                                                                                                                                                                                                               |

|           | Related I TION 2. TION 3. CPU Pine 60x Bus MPX Bus Cache Co Specific Multi-GT CPU Bus PowerPC TION 4. Pinout D Memory SDRAM I ECC Sup Memory TION 5. P2P Cap PCI Arbit Delayed 32-bit PC Cache Co | TION 3. CPU INTERFACE FUNCTIONAL OVERVIEW  CPU Pinout Description  60x Bus Mode  MPX Bus Mode  Cache Coherency  Specific CPUs Aspects  Multi-GT or Multi-slave Modes  CPU Bus Multiple Masters  PowerPC COP/JTG Interface  TION 4. SDRAM INTERFACE FUNCTIONAL OVERVIEW  Pinout Description  Memory Connection  SDRAM Address Control  SDRAM Initialization  ECC Support.  Memory Banks and Pages |

| SEC  | ECTION 6. DEVICE INTERFACE FUNCTIONA | AL OVERVIEW51           |

|------|--------------------------------------|-------------------------|

| 6.1  | Device Connection                    | 51                      |

| 6.2  | 2 8-bit Device                       | 53                      |

| 6.3  | 3 16-bit Device                      | 55                      |

| 6.4  | 32-bit Device                        | 56                      |

| 6.5  | 5 Signals Timing                     | 58                      |

| 6.6  | Ready Support                        | 59                      |

| 6.7  | 7 Syncburst SRAM                     | 60                      |

| SEC  | ECTION 7. COMMUNICATION INTERFACE F  | UNCTIONAL OVERVIEW61    |

| 7.1  | Ethernet Controllers                 | 61                      |

| 7.2  | 2 MPSC Controllers                   | 62                      |

| 7.3  | B Cache Coherency                    | 62                      |

| 7.4  | MPSC and Ethernet SW Implications    | 63                      |

| 7.5  | 5 I2C Interface                      | 70                      |

| 7.6  | Baud Rate Generator                  | 72                      |

| SEC  | ECTION 8. MULTI-PURPOSE PIN INTERFAC | E FUNCTIONAL OVERVIEW74 |

| 8.1  | General Purpose Pin (GPP)            | 74                      |

| 8.2  | 2 Interrupt Outputs                  | 75                      |

| 8.3  | B PCI Arbiter                        | 76                      |

| 8.4  | I DMA Request                        | 76                      |

| 8.5  | 5 DMA acknowledge                    | 76                      |

| 8.6  | Unified Memory Architecture Control  | 77                      |

| 8.7  | DMA End of Transfer                  | 77                      |

| 8.8  | B Timer Counter Enable               | 77                      |

| 8.9  | Initialization Active                | 77                      |

| 8.10 | 10 BRG Clock                         | 77                      |

| SECTION 9.      | JTAG INTERFACE FUNCTIONAL OVERVIEW       | 78    |

|-----------------|------------------------------------------|-------|

| SECTION 10.     | IDMA UNIT FUNCTIONAL OVERVIEW            | 79    |

| 10.1 Chain Mo   | de                                       | 81    |

| 10.2 Cache Co   | pherency                                 | 81    |

| SECTION 11.     | INTERRUPT CONTROLLER FUNCTIONAL OVERVIEW | 82    |

| 11.1 Using Ex   | ternal Interrupt Controller              | 86    |

| SECTION 12.     | MESSAGING UNITS FUNCTIONAL OVERVIEW      | 87    |

| 12.1 Messagi    | ng                                       | 87    |

| 12.2 Doorbell   |                                          | 87    |

| 12.3 Circular   | Queue                                    | 88    |

| SECTION 13.     | DESIGN CONSIDERATION OVERVIEW            | 90    |

| SECTION 14.     | CPU INTERFACE DESIGN CONSIDERATIONS      | 91    |

| 14.1 CPU Inter  | face Connectivity                        | 91    |

| 14.2 Electrical | Specification                            | 92    |

| 14.3 Terminati  | on Topology                              | 92    |

| 14.4 Timing R   | equirements                              | 92    |

| 14.5 Layout In  | structions                               | 104   |

| SECTION 15.     | SDRAM INTERFACE DESIGN CONSIDERATIONS    | . 106 |

| 15.1 Interface  | Connectivity                             | 106   |

| 15.2 Electrical | Specification                            | 106   |

| 15.3 Terminati  | on Topology                              | 106   |

| 15.4 Timing Ro  | equirements                              | 109   |

| 15.5 Layout In  | structions                               | 126   |

| SECTION 16.     | PCI Interface Design Considerations      | . 128 |

| 16.1 Interface  | Connectivity                             | 128   |

| 16.2 Electrical | Definition                               | 128   |

| 16.3 Termination Topology                             | 128 |

|-------------------------------------------------------|-----|

| 16.4 Timing Requirements                              | 128 |

| 16.5 Layout Instructions                              | 133 |

| Section 17. Ethernet Interface Design Considerations1 | 134 |

| 17.1 Interface Connectivity                           | 134 |

| 17.2 Electrical Specification                         | 135 |

| 17.3 Termination Topology                             | 135 |

| 17.4 Timing Requirements                              | 135 |

| 17.5 Layout Instructions                              | 138 |

| SECTION 18. POWER SUPPLY1                             | 140 |

| 18.1 De-coupling Recommendations                      | 140 |

| SECTION 19. CLOCKS1                                   | 143 |

| Section 20. Reset1                                    | 144 |

| 20.1 Reset Configurations                             | 144 |

| SECTION 21. BRINGING UP THE SYSTEM (DEBUGGING)1       | 145 |

| 21.1 Communication Unit                               | 145 |

| SECTION 22. REVISION HISTORY1                         | 146 |

| APPENDIX A. I2C EEPROM EXAMPLE1                       | 147 |

| APPENDIX B. SDRAM MODE REGISTER/CODE1                 | 149 |

| APPENDIX C. ECC INITIALIZATION- EXAMPLE CODE          | 150 |

| C.1 Assembler Code150                                 |     |

| C.2 C Code Example151                                 |     |

| APPENDIX D. BIG AND LITTLE ENDIAN SUPPORT1            | 152 |

| D.1 Internal Register152                              |     |

| D.2 Communication Descriptors152                      |     |

| D.3        | PCI Interface                        | . 153 |

|------------|--------------------------------------|-------|

| D.4        | Swapping Options                     | . 153 |

| АРР        | PENDIX E. COMMUNICATION EXAMPLE CODE | 158   |

| E.1        | Ethernet Initialization              | . 158 |

| E.2        | Ethernet API                         | . 159 |

| <b>E.3</b> | MPSC API                             | . 160 |

# **List of Tables**

| Table 1:  | CPU Interface Pin Information                                                       | 14  |

|-----------|-------------------------------------------------------------------------------------|-----|

| Table 2:  | GT-64260A Supported Features in MPX Bus Mode                                        |     |

| Table 3:  | IDMA Address Base/Top Registers                                                     |     |

| Table 4:  | PCI Address Base/Top Registers                                                      |     |

| Table 5:  | Multi-GT Device ID                                                                  |     |

| Table 6:  | Multi-GT Mode Transaction Translation                                               |     |

| Table 7:  | SDRAM Interface Pinout Description                                                  |     |

| Table 8:  | SDRAM Interface Pinout Description                                                  |     |

| Table 9:  | SDRAM Memory Space                                                                  |     |

|           | ECC Bank Selection                                                                  |     |

|           | PCI P2P Configuration Register Initialization Example                               |     |

|           | Internal PCI Arbiter in Multiplexing                                                |     |

|           | CPU Interface Configuration at Reset                                                |     |

|           | Typical CPU AC Timings                                                              |     |

|           | Single-GT and Single CPU AC Timing                                                  |     |

| Table 16: | Single-GT and Multiple CPU AC Timing                                                | 98  |

|           | Multiple GT-64260As and a Single CPU AC Timing                                      |     |

|           | Signal Topology Categories                                                          |     |

|           | Trace Length for Data Topologies                                                    |     |

| Table 20: | GT-64260A SDRAM Interface AC Timing                                                 | 115 |

| Table 21: | Typical SDRAM Interface AC Timing                                                   | 115 |

| Table 23: | GT-64260A CS AC Timing                                                              | 121 |

| Table 24: | Typical SDRAM CS AC Timing                                                          | 121 |

| Table 22: | Trace Length for Data Topologies                                                    | 121 |

| Table 25: | Trace Length for Double Cycle Signal Topologies                                     | 124 |

| Table 26: | GT-64260A Double Cycle Signals AC Timing                                            | 125 |

| Table 27: | Typical SDRAM CS AC Timing                                                          | 125 |

| Table 28: | PCI AC Timing for 33 MHz and 66 MHz (From the PCI Specification Document, Rev. 2.2) | 129 |

| Table 29: | GT-64260A PCI Interface AC Timing                                                   | 129 |

| Table 30: | RMII AC timing for 50 MHz (from RMII Specification Rev. 1.2 Document)               | 136 |

| Table 31: | Ethernet RMII Interface                                                             | 136 |

| Table 32: | GT-64260A Voltages                                                                  | 140 |

| Table 33: | Revision History                                                                    | 146 |

| Table 34: | Big and Little Endian Bit Ordering                                                  | 152 |

| Table 35: | PCI Big Endian Bit Ordering                                                         | 153 |

| Table 36: | Data Swapping                                                                       | 154 |

| Table 37: | Master Swapping                                                                     | 155 |

| Table 38: | Master Swapping (on the SDRAM bus.                                                  | 156 |

| Table 39: | Swapping for All Eight Options                                                      | 156 |

# **List of Figures**

| Figure 1: GT-64260A Interfaces                                            | 12 |

|---------------------------------------------------------------------------|----|

| Figure 2: Typical GT-64260A System Configuration                          | 13 |

| Figure 3: PCI Reads from Cache Coherent Regions                           | 19 |

| Figure 4: PPC750FX CPU Keeper                                             | 23 |

| Figure 5: Multi-GT System Architecture                                    | 25 |

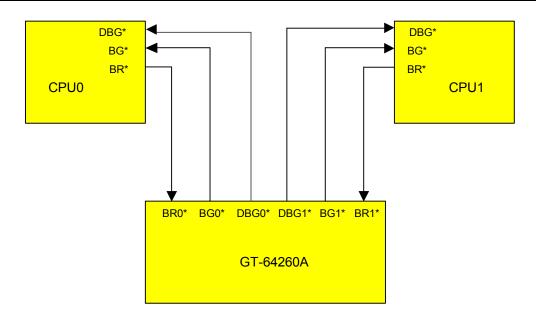

| Figure 6: 2 CPUs Connection Through Internal 60x Arbiter                  | 27 |

| Figure 7: Two CPUs Connected Through an External Arbiter                  | 28 |

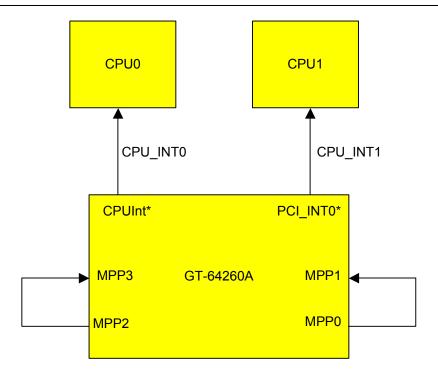

| Figure 8: Interrupt Pins' Connectivity                                    | 30 |

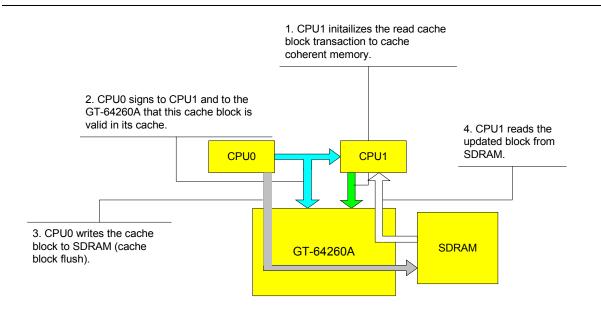

| Figure 9: CPU to CPU Cache Coherency Data Flow                            | 30 |

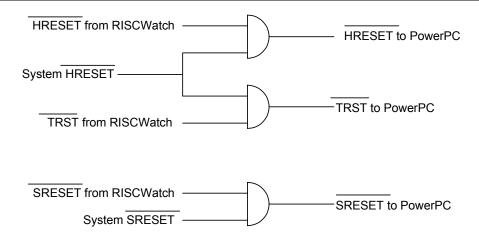

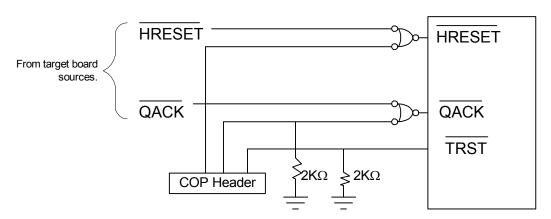

| Figure 10: IBM RISCWatchTM JTAG to HRESET, TRST, and SRESET pin Connector | 31 |

| Figure 11: Motorola JTAG to HRESET and TRST pin Connector                 | 31 |

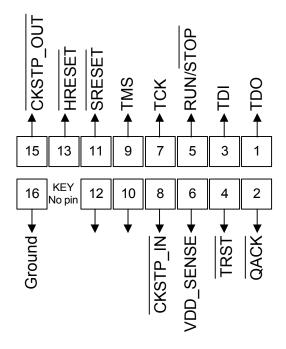

| Figure 12: JTAG/COP 16 Pin Connectors                                     | 32 |

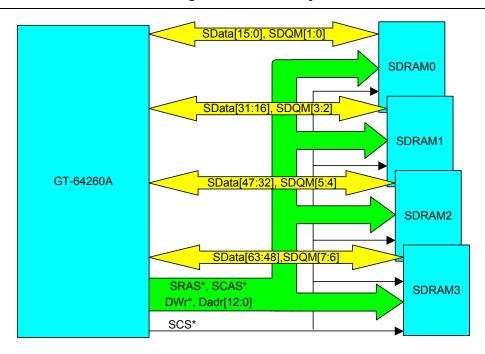

| Figure 13: SDRAM Connection for Regular SDRAM/Heavy Load Mode             | 37 |

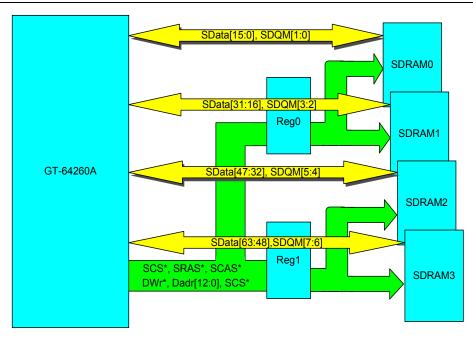

| Figure 14: SDRAM Connection for Registered SDRAM Mode                     | 38 |

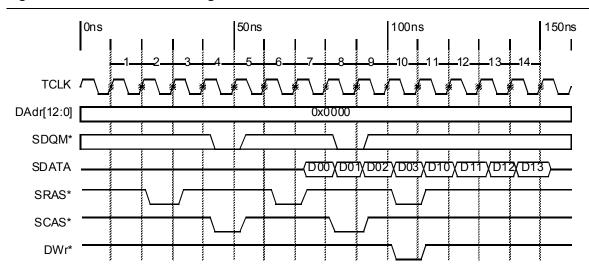

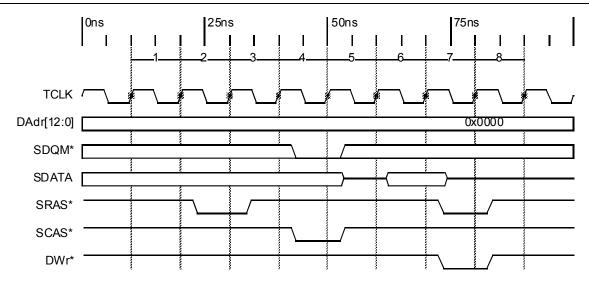

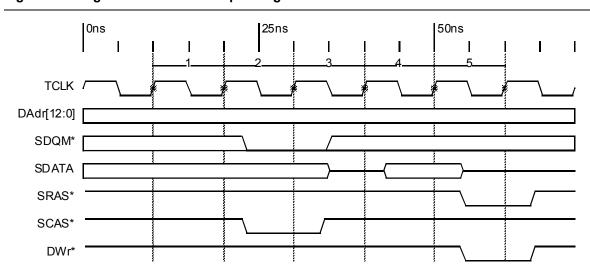

| Figure 15: Two Read Interleaving from Different Virtual Banks             | 43 |

| Figure 16: Single Read Access to Non-open Page                            | 44 |

| Figure 17: Single Read Access to Open Page                                | 44 |

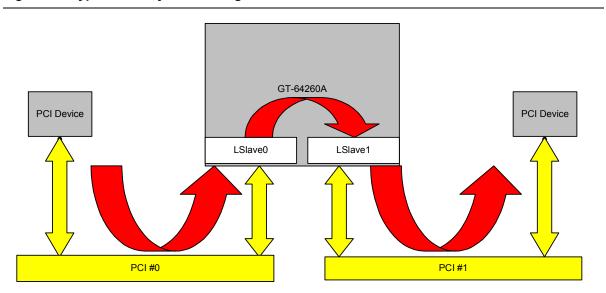

| Figure 18: Typical P2P System Configuration                               | 46 |

| Figure 19: I/O P2P Transaction Example                                    | 47 |

| Figure 20: Three Device Connection Example                                | 52 |

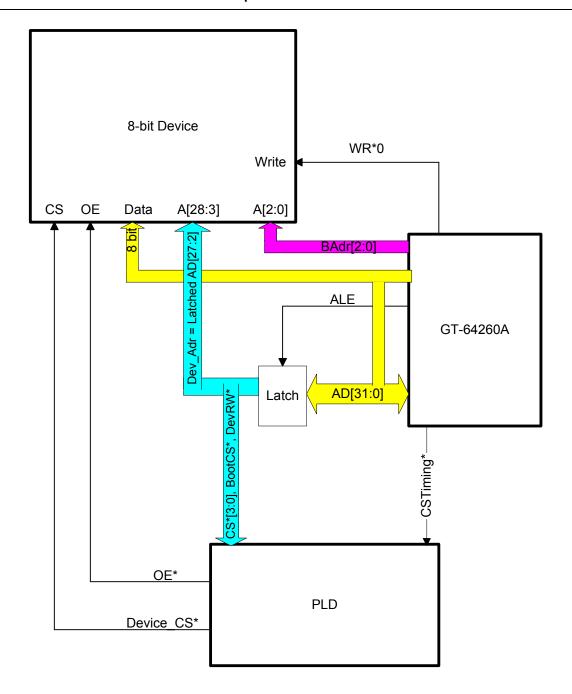

| Figure 21: 8-bit Device Connection Example                                | 54 |

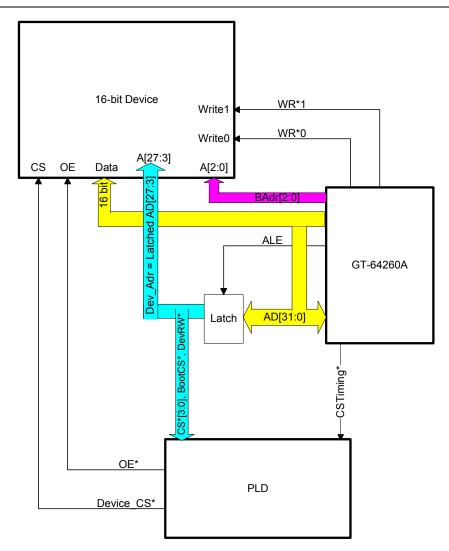

| Figure 22: 16-bit Device Connection Example                               | 55 |

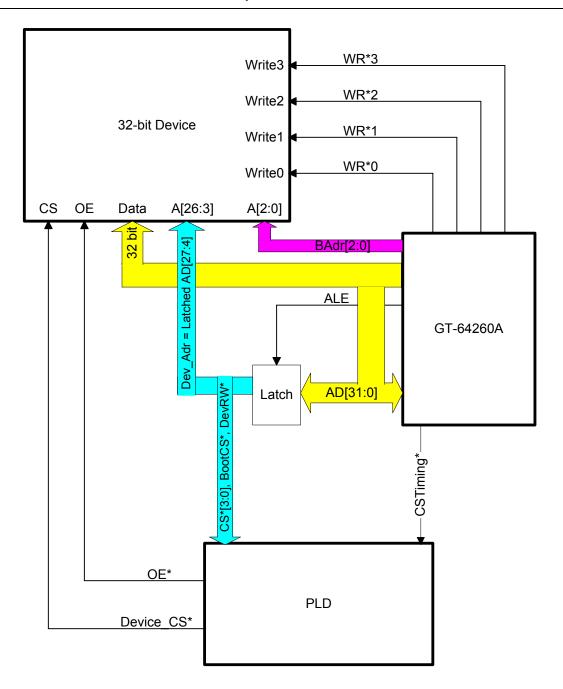

| Figure 23: 32-bit Device Connection Example                               | 57 |

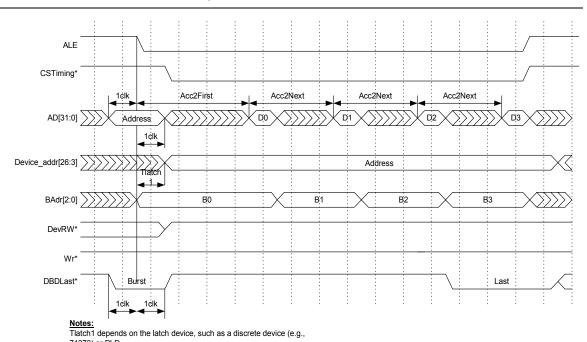

| Figure 24: Device Burst Read Example                                      | 58 |

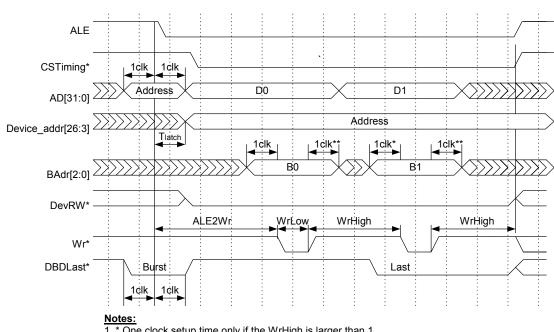

| Figure 25: Device Burst Write Example                                     | 59 |

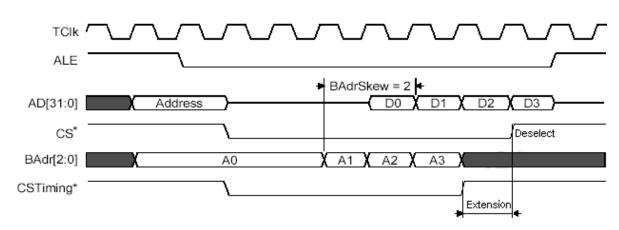

| Figure 26: SCD Pipeline Sync Burst SRAM Read Example                      | 60 |

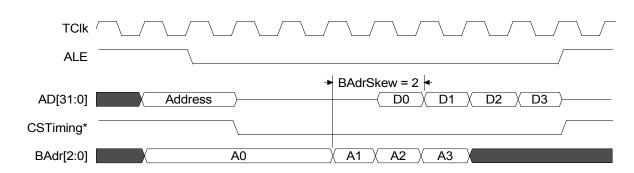

| Figure 27: DCD Pipeline Sync Burst SRAM Read Example                      | 60 |

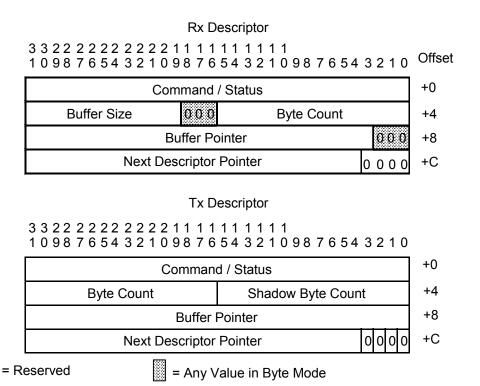

| Figure 28: SDMA Descriptor Format                                         | 63 |

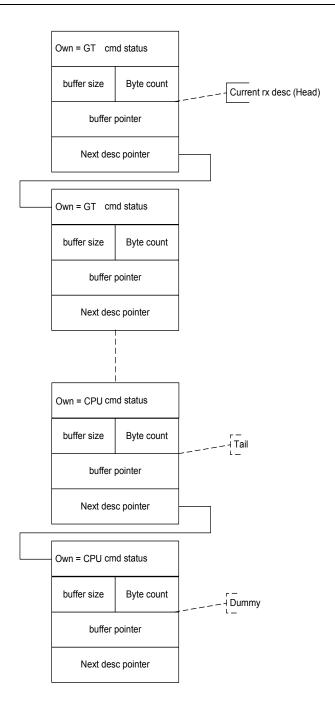

| Figure 29: Rx Descriptor Chain                                            | 65 |

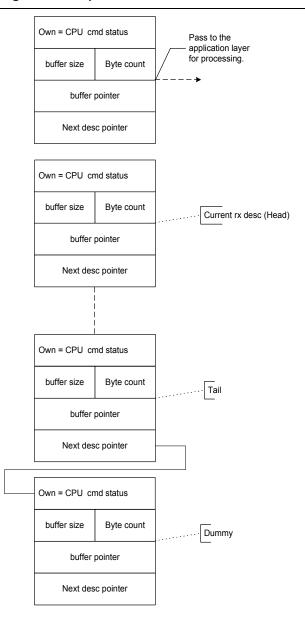

| Figure 30: Disconnecting the Descriptor Chain                             | 66 |

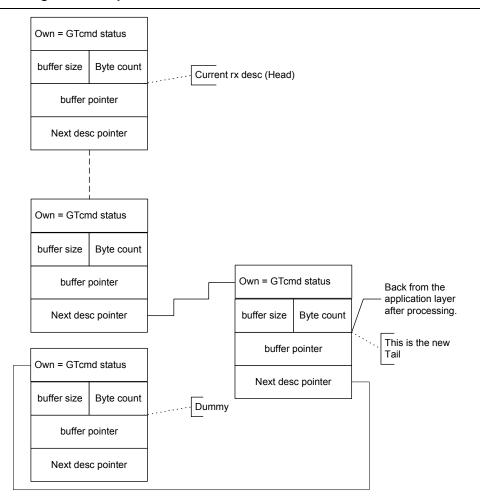

| Figure 31: Releasing the Descriptor Chain                                 | 67 |

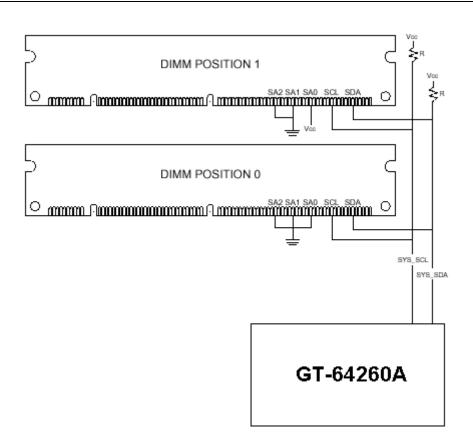

| Figure 32: GT-64260A I2C Interface Connection to SDRAM DIMMS              |    |

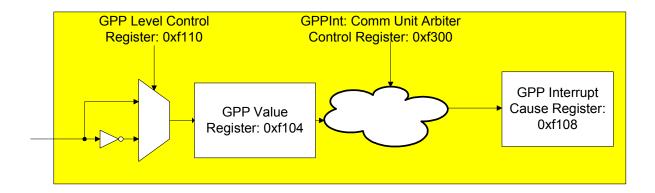

| Figure 33: GPP Configured as Input                                        |    |

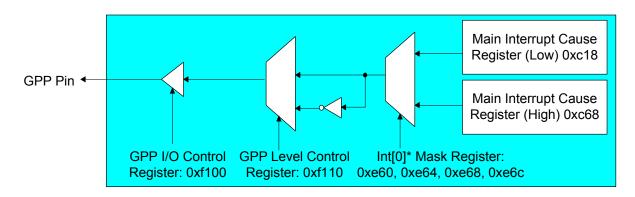

| Figure 34: MPP Interrupt Outputs                                          |    |

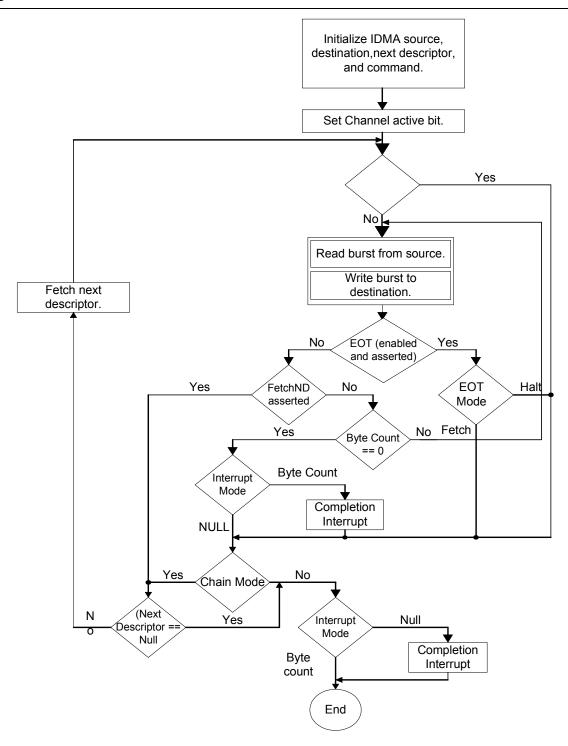

| Figure 35: DMA Controller General Flow                                    |    |

| Figure 36: Interrupt Routing Example                                      |    |

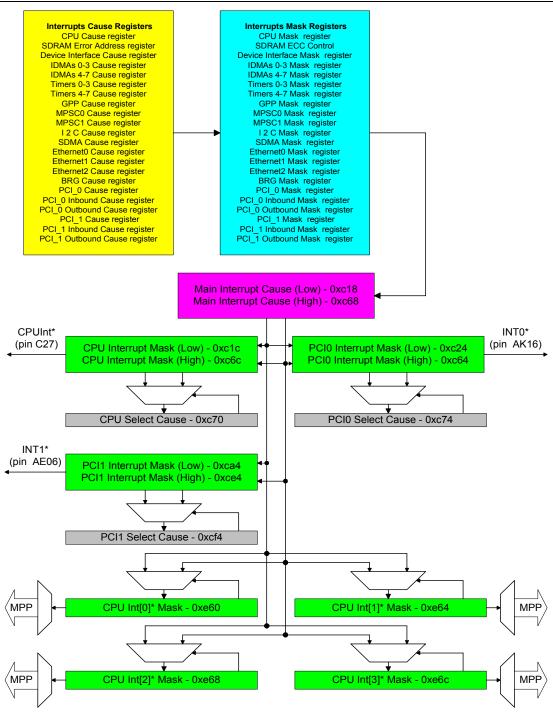

| Figure 37: GT-64260A Interrupt Routing Architecture                       |    |

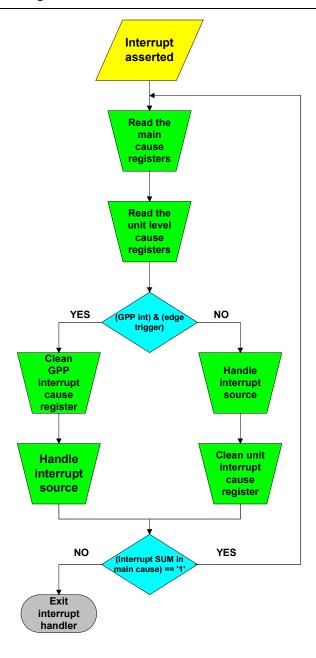

| Figure 38: Interrupt Handling Procedure                                   |    |

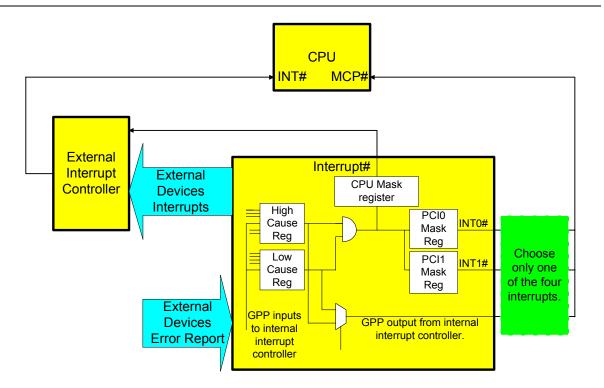

| Figure 39: External Interrupt Controller                                  |    |

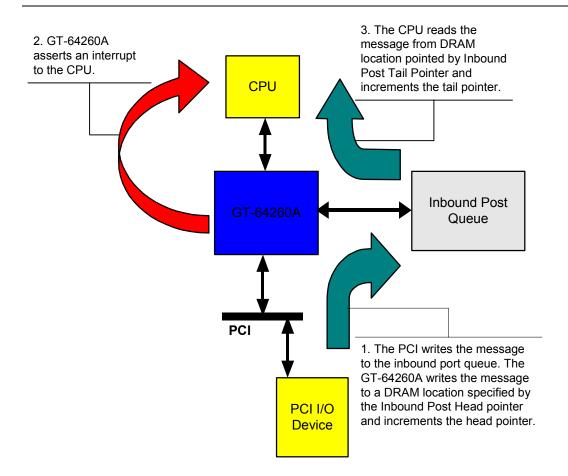

| Figure 40: Inbound Circular Queue                                         |    |

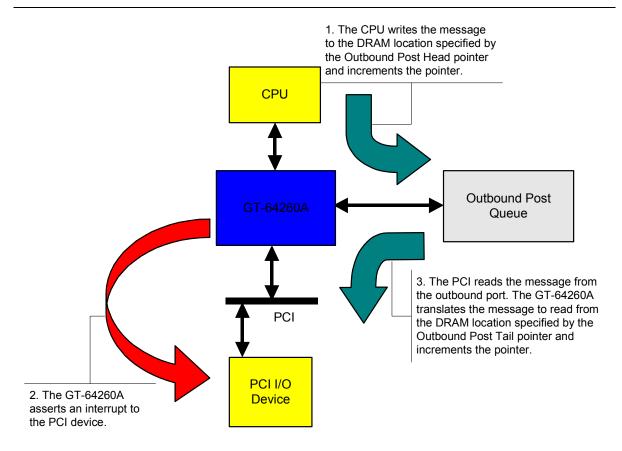

| Figure 41: Outbound Circular Queue                                        |    |

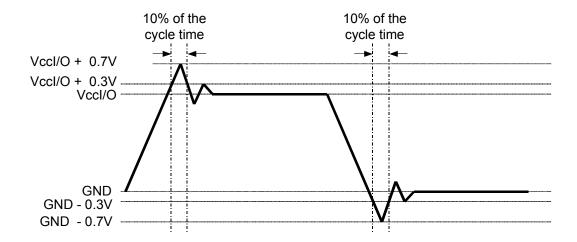

| Figure 42: GT-64260A Overshoot/Undershoot Voltage                         |    |

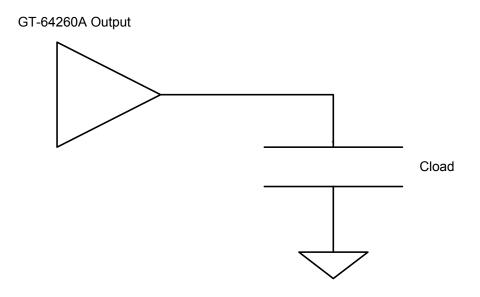

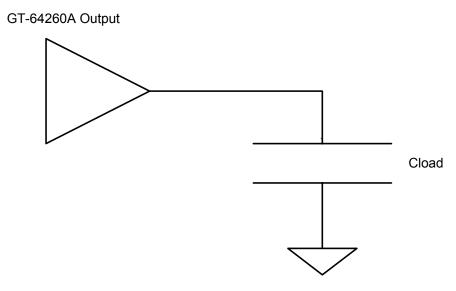

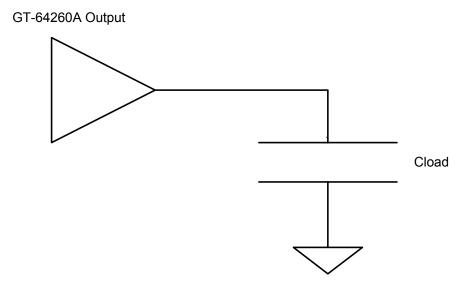

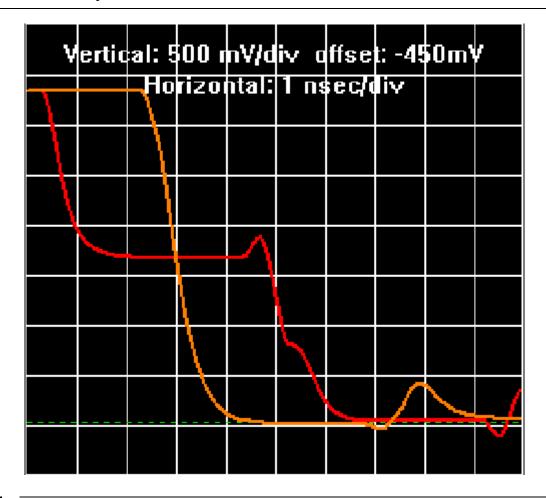

| Figure 43: GT-64260A Test Circuit (Cload = 15pf)                          | 92 |

|                                                                           |    |

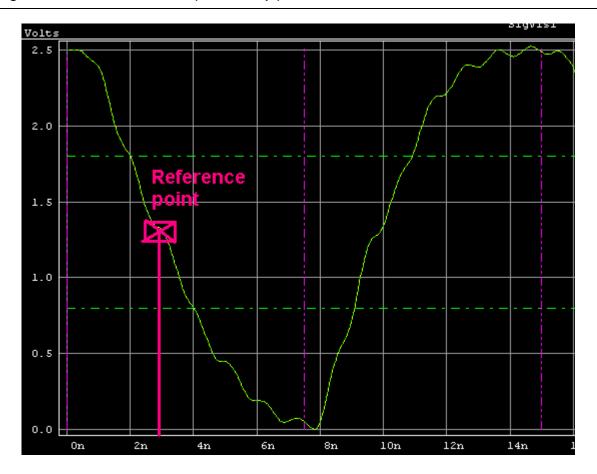

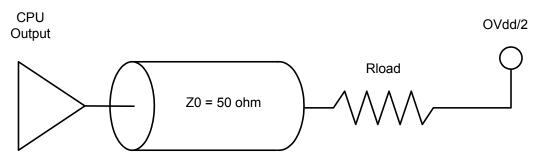

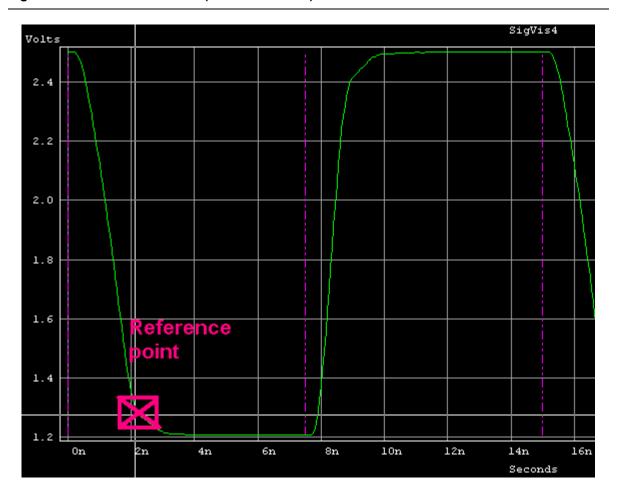

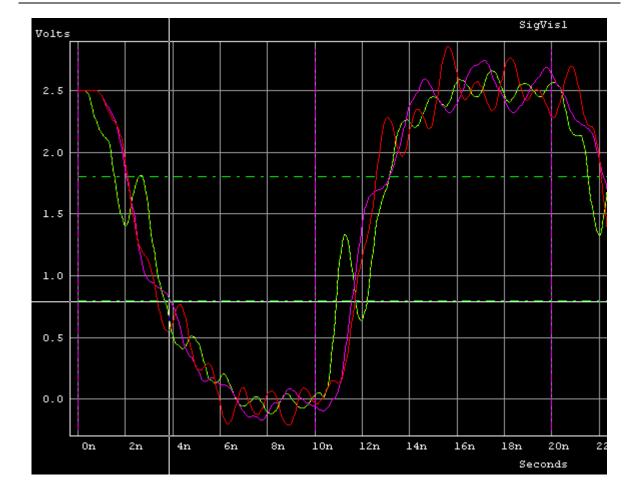

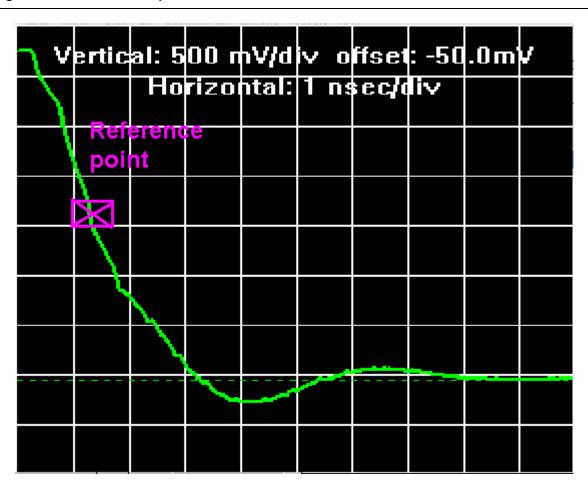

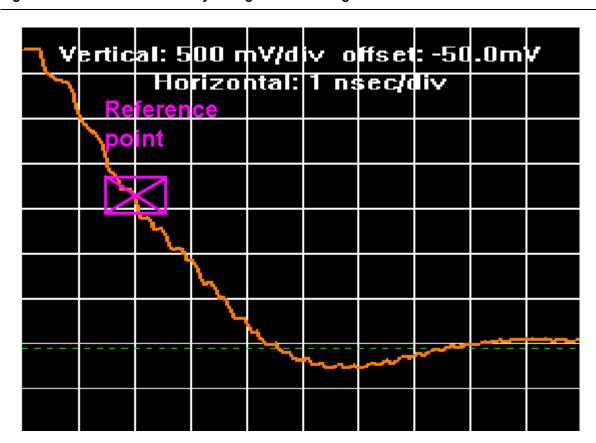

| Figure 44: Test Circuit Results (Cload = 15pf)                              | 93  |

|-----------------------------------------------------------------------------|-----|

| Figure 45: GT-64260A Test Circuit (Rload = 50 Ohm)                          | 94  |

| Figure 46: Test Circuit Results (Rload = 50 Ohm)                            | 94  |

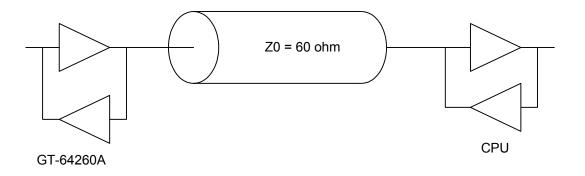

| Figure 47: GT-64260A to CPU Point-to-Point Configuration                    | 95  |

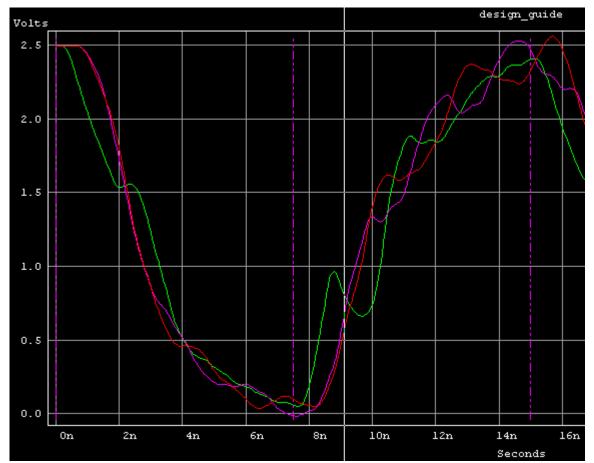

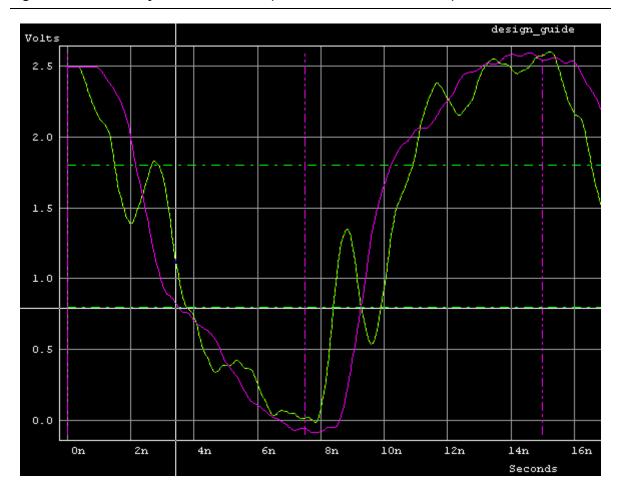

| Figure 48: 1 ns Delay Trace Simulation                                      | 96  |

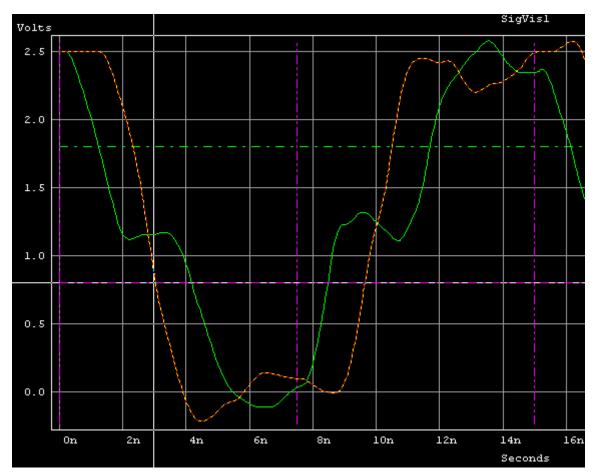

| Figure 49: 0.8 ns Delay Trace Simulation                                    | 97  |

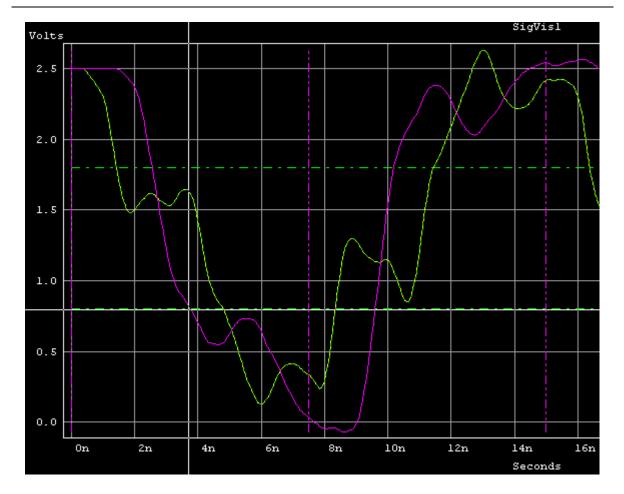

| Figure 50: GT-64260A to Multiple CPU Configuration                          | 98  |

| Figure 51: 0.5 ns Delay Trace Simulation (Maximum Distance 2.5 Inches)      | 99  |

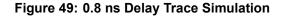

| Figure 52: 0.5 ns Delay Trace Simulation (Maximum Distance 4 Inches)        | 100 |

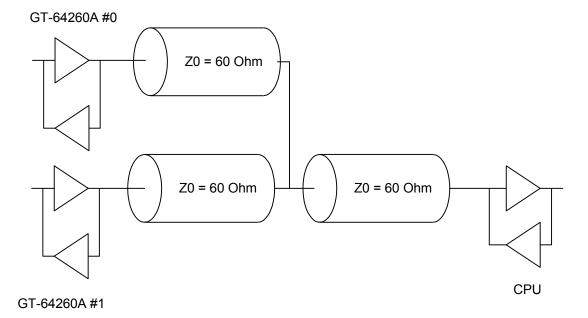

| Figure 53: Multiple GT-64260As to a Single CPU Configuration                | 101 |

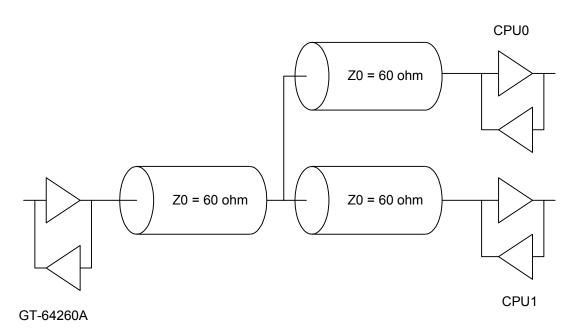

| Figure 54: 1.1 ns Delay Trace Simulation                                    | 102 |

| Figure 55: 0.8 ns Delay Trace Simulation                                    | 103 |

| Figure 56: Layout for a Single GT-64260A to a Single CPU                    | 104 |

| Figure 57: Layout for a Single GT-64260A to Multiple CPUs                   | 105 |

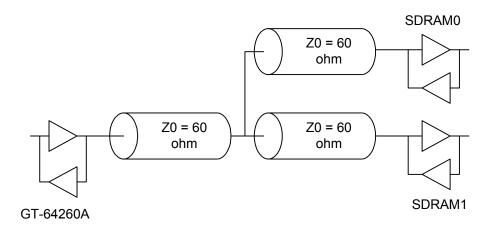

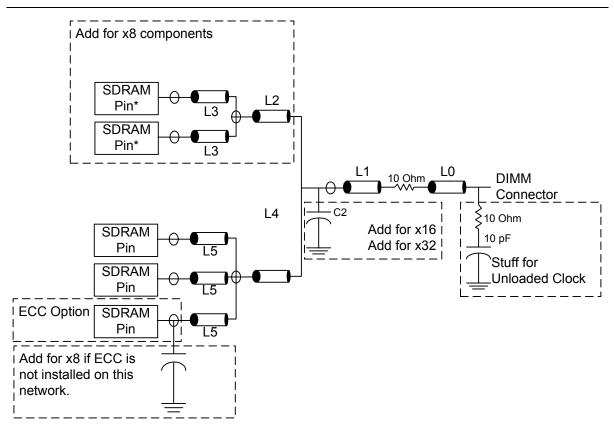

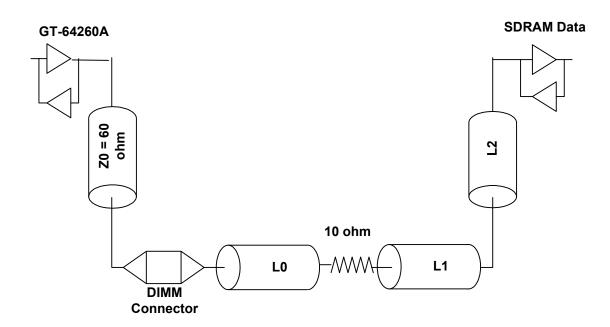

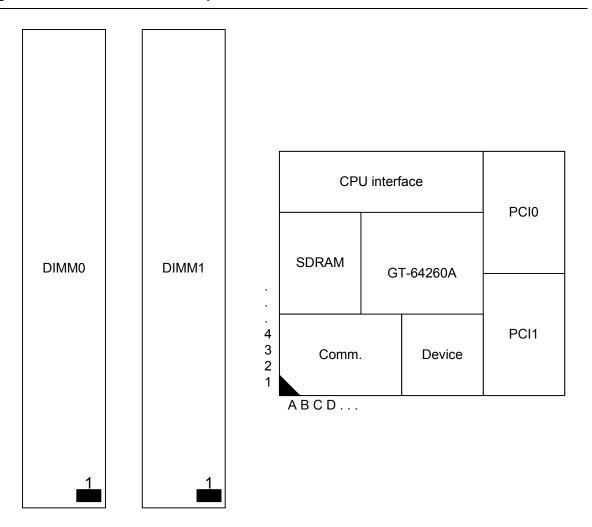

| Figure 58: SDRAM Configuration Example                                      | 107 |

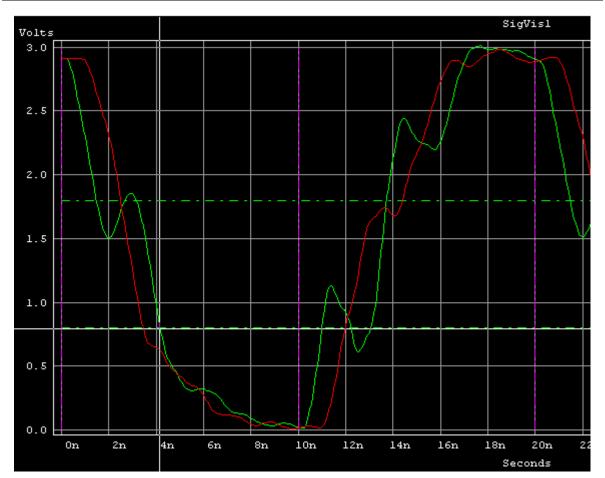

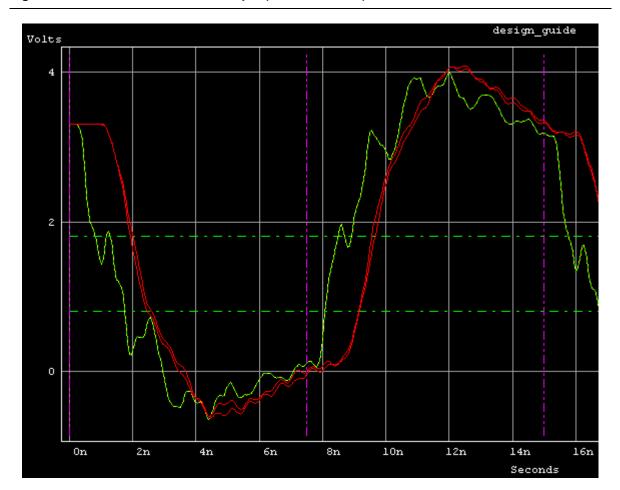

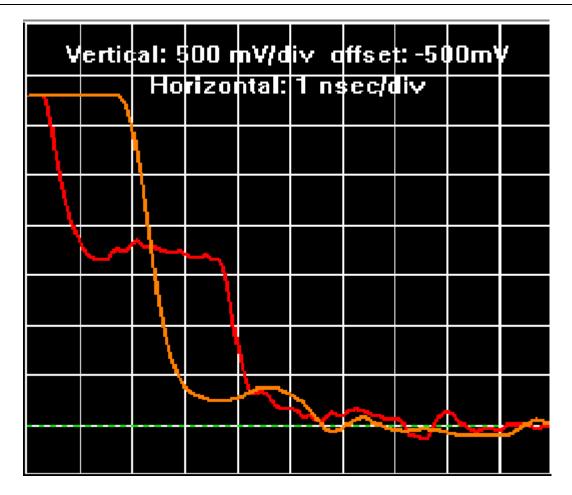

| Figure 59: SDRAM Simulation Example                                         | 107 |

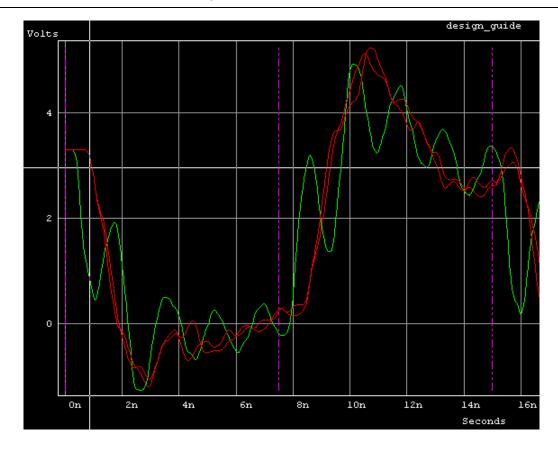

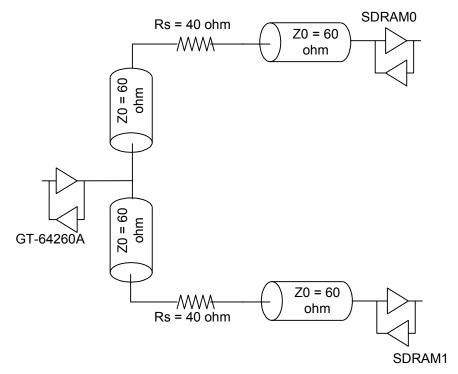

| Figure 60: SDRAM Configuration Example (With Resistors)                     | 108 |

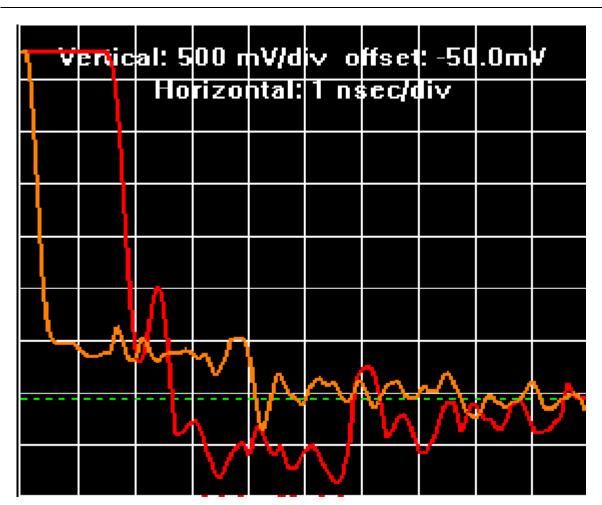

| Figure 61: SDRAM Simulation Example (With Resistors)                        | 109 |

| Figure 62: DIMM Clock Topology                                              | 111 |

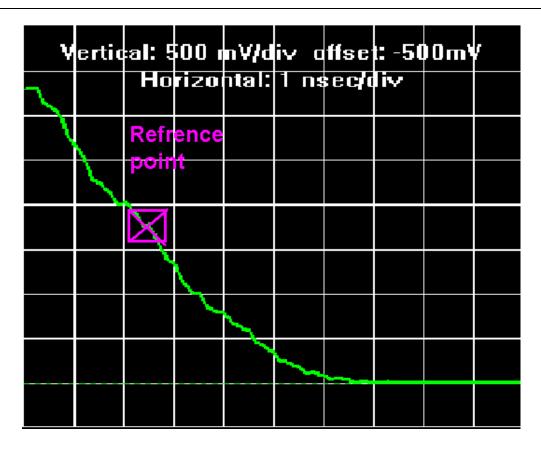

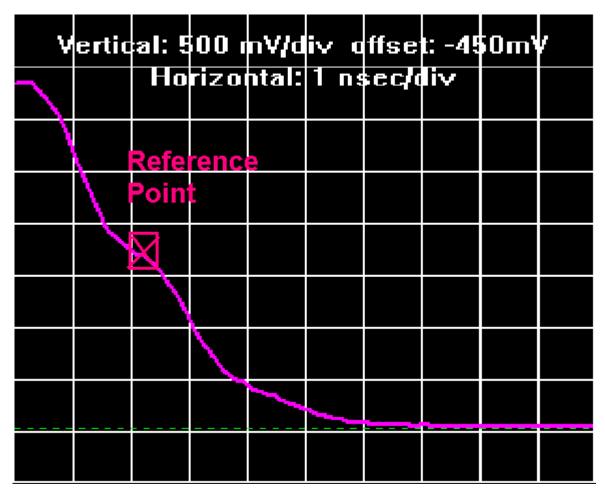

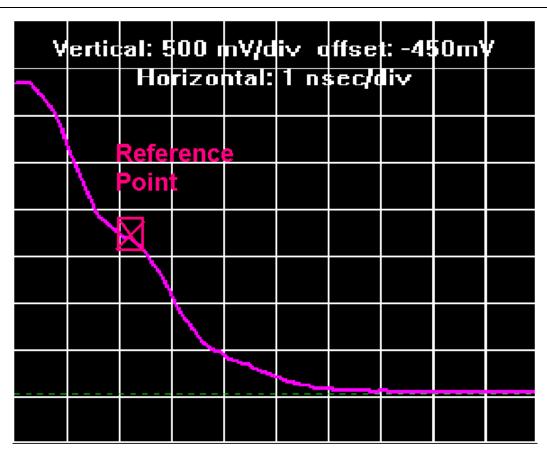

| Figure 63: GT-64260A Data Reference Point                                   | 112 |

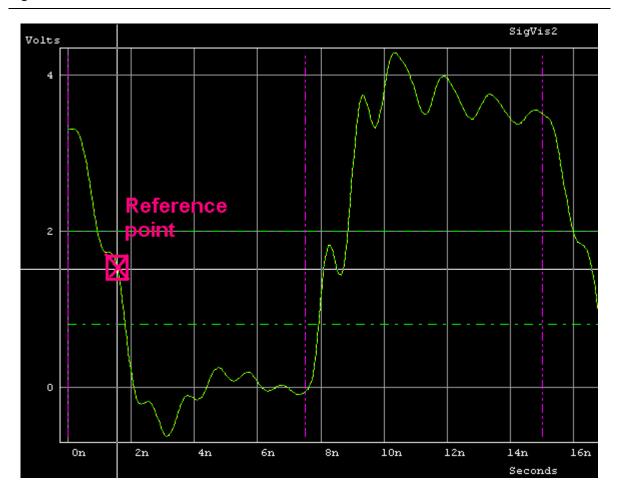

| Figure 64: SDRAM Data Reference Point                                       | 113 |

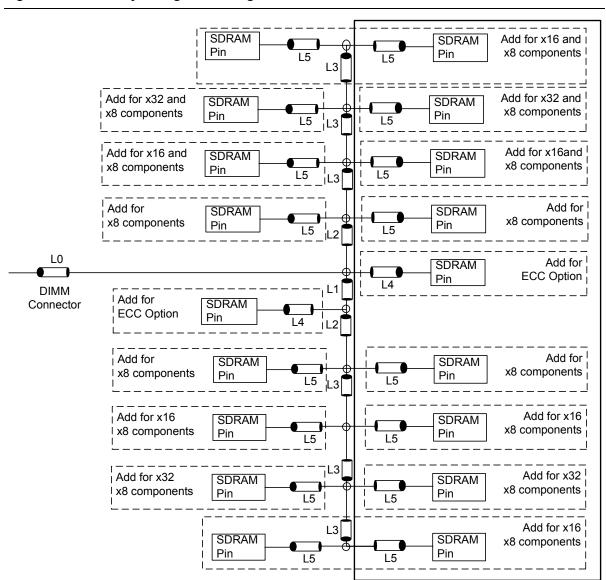

| Figure 65: Selected Memory Configuration Data Topology                      | 114 |

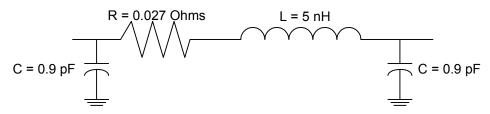

| Figure 66: DIMM Connector Package Model                                     | 115 |

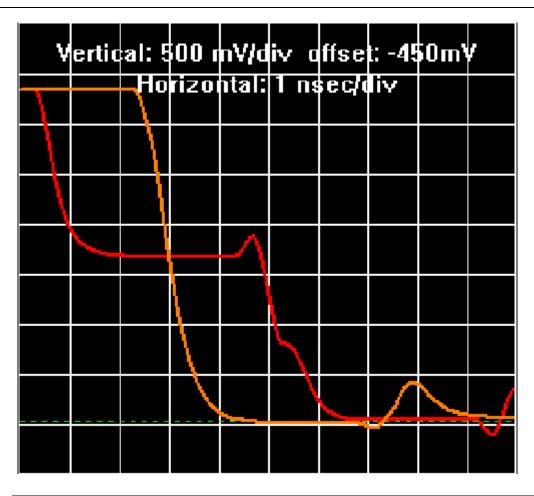

| Figure 67: 0.8 ns Delay Trace Simulation (2.1 ns Fly Time Reference Point)  | 116 |

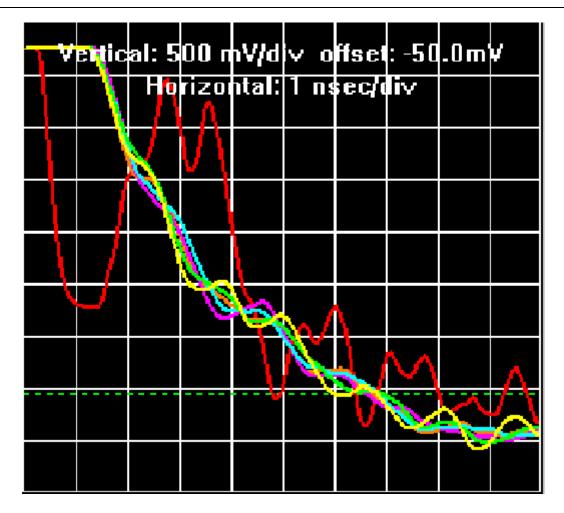

| Figure 68: 0.8 ns Delay Trace Simulation (1.54 ns Fly Time Reference Point) | 117 |

| Figure 69: GT-64260A Test Circuit (Cload = 50pf)                            | 118 |

| Figure 70: GT-64260A Chip Select Reference Point                            | 119 |

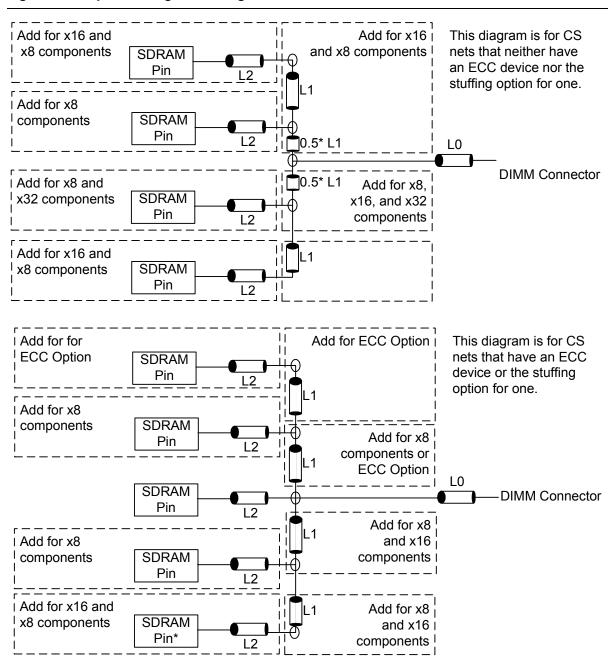

| Figure 71: Chip Select Signal Routing on the DIMM Module                    | 120 |

| Figure 72: 0.8 ns Delay Trace Simulation (2.8 ns Fly Time Reference Point)  | 122 |

| Figure 73: GT-64260A Double Cycle Signals AC Timing                         | 123 |

| Figure 74: Double Cycle Signal Routing on the DIMM Module                   | 124 |

| Figure 75: 0.8 ns Delay Trace Simulation (2.0 ns Fly Time Reference Point)  | 126 |

| Figure 76: Device Placement Example                                         | 127 |

| Figure 77: GT-64260A Test Circuit (Cload = 20pf)                            | 131 |

| Figure 78: GT-64260A GNT* Signals Reference Point                           | 132 |

| Figure 79: 2.1 ns Fly Time Reference Point                                  | 133 |

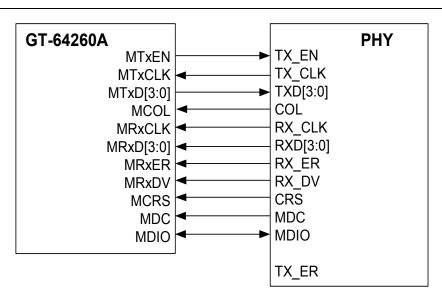

| Figure 80: MII Interface Connection                                         | 134 |

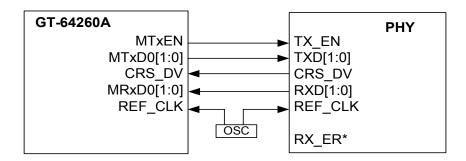

| Figure 81: RMII Interface Connection:                                       | 135 |

| Figure 82: GT-64260A RMII Signals Reference Point                           | 137 |

| Figure 83: 2.1 ns Fly Time Reference Point                                  | 138 |

| Figure 84: PHY Placement                                                    | 139 |

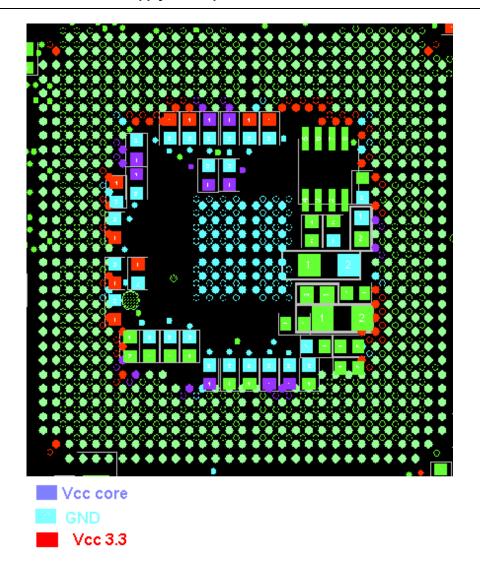

| Figure 85: GT-64260A Power Supply Pin Map                                   | 142 |

# **Section 1. Introduction**

This design guide provides information for designing a system using the GT-64260A. This guide is intended for internal and external reference and is subject to future changes and modifications.

Use this document as an addition to the GT-64260A datasheet and evaluation/reference design schematics.

## 1.1 Related Documentation

The following documents are referenced by this design guide or provide additional information about working with the GT-64260A. See the Marvell® website at <a href="http://www.marvell.com">http://www.marvell.com</a> to access this material.

- GT-64260A Datasheet, Doc. No. MV-S100413-00

- EV-64260A-BP-xxxxx Reference Platform Schematics

- PCI 2.2 Local Bus Specification

- AN-66: Initializing Ethernet Ports

- AN-67: Powering Up /Powering Down Galileo Technology Devices with Multiple Power Supplies of Different Voltages, Doc. No. MV-S300069-00

- AN-72: Operating the MPSC as a UART, Doc. No. MV-S300072-00

- AN-82: SDRAM Clocking Schemes in the GT-642xx/A Devices, Doc. No. MV-S300108-00

- BRG Settings Tool

- PCI Specification 2.2 http://www.pcisig.com/specifications/conventional\_pci

# Section 2. GT-64260A Overview

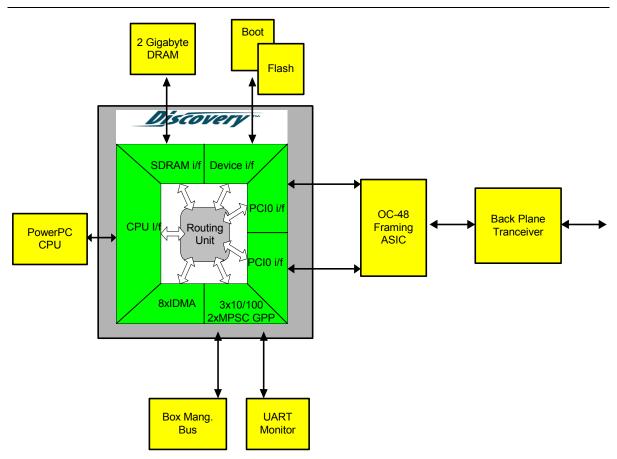

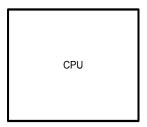

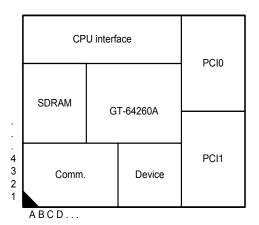

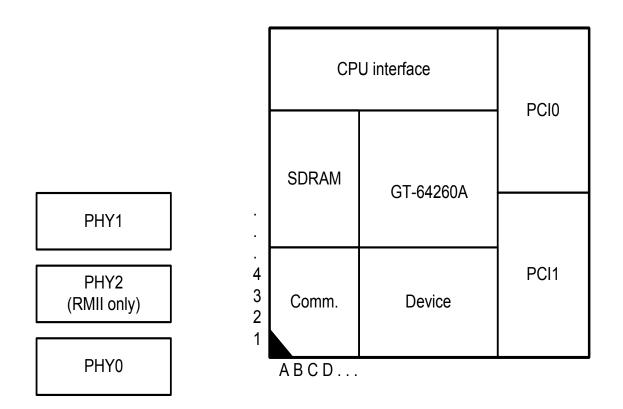

The GT-64260A is a bridge from the PowerPC processor to the PCI bus, as well as a high-speed memory controller for external ROM and external peripherals. In addition, the GT-64260A integrates three 10/100 Mbps Ethernet ports and two MPSC controllers.

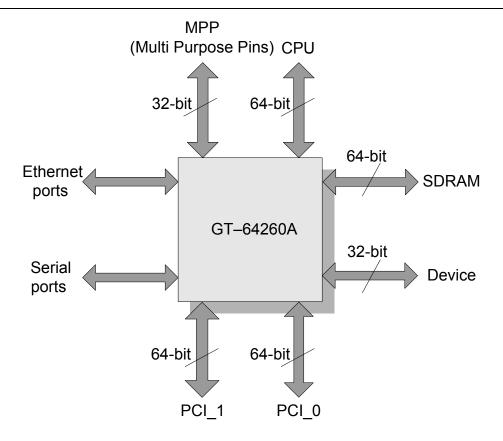

The GT-64260A provides a single-chip solution for designers building systems for a PowerPC 64-bit bus CPU. It has the following interfaces:

- A 64-bit interface to the CPU bus.

- A 64-bit interface to SDRAM.

- A 32-bit interface to devices (various types of memory and I/O devices).

- Two 64-bit PCI interfaces.

- Three RMII/MII interfaces.

- Two MPSC communication interfaces.

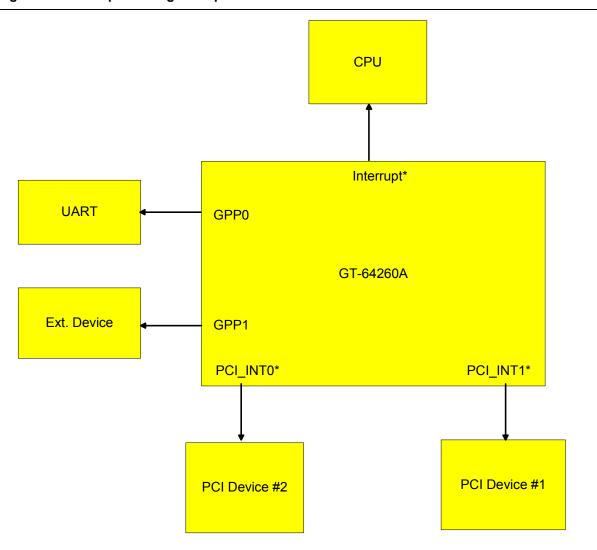

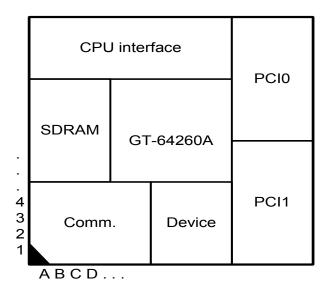

Figure 1 shows the GT-64260A interfaces.

Figure 1: GT-64260A Interfaces

Figure 2: Typical GT-64260A System Configuration

# Section 3. CPU Interface Functional Overview

The GT-64260A supports PowerPC 64-bit bus CPUs. (See Section 3.5 "Specific CPUs Aspects" .) These include the following:

- Motorola MPC603e/604e

- Motorola MPC740/750/755

- Motorola PowerQUICC II (MPC8260)

- Motorola MPC7400/7410/745x

- IBM PPC603e

- IBM PPC750/750cx/e/750FX

- Any 64-bit 60x or MPX compatible CPU

The CPU interface can work as a slave interface, responding to CPU transactions, or as a master interface, generating transactions on the CPU bus. The master interface is used for PowerPC snoop generation. It also allows for access to MPC8260 local memory or GT-to-GT transfers in a multi-GT-64260A configuration.

# 3.1 CPU Pinout Description

The GT-64260A provides all the pins needed to interface between the PowerPC processor and other devices (such as SDRAM, ROM, PCI, etc.). Generally, there is a point-to-point connection between the GT-64260A and the CPU. In other cases, it depends on the system architecture, such as multi-GT-64260A, multiple CPU, or external arbiter. The following table describes the pin information and details of the GT-64260A CPU interface.

Table 1: CPU Interface Pin Information

| Pin Name                          | Input/<br>Output | PowerPC CPU Pin<br>Connection                                                                                                                                                     | Required<br>External<br>Resistor          | Description                                                                                                                                                       |

|-----------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[0-31],<br>AP[0-4]               | T/S I/O          | For address connection to CPUs that support 36-bit addressing, see 3.5.3 "MPC745x Extended Pins" on page 22. For all other CPUs with 32-bit address, connect to A[0-31], AP[0-4]. | 10K-Ohm Pull-up                           | CPU address bus and address parity bus. To work with address parity in the system, set the CPU Configuration register's APValid bit [26], at offset 0x000 to '1'. |

| DH[0-31],<br>DL[0-31],<br>DP[0-7] | T/S I/O          | Some CPUs use D[0-63] for the entire data bus. In this case, use the following connection:  DH[0-31] = D[0-31]  DL[0-31]=D[32-63]                                                 | The GT-64260A includes internal Pull-ups. | CPU data bus and data parity bus. To work with data parity in the system, set the CPU Configuration register's DPValid bit [19], at offset 0x000 to '1'.          |

Table 1: CPU Interface Pin Information (Continued)

| Pin Name  | Input/<br>Output | PowerPC CPU Pin<br>Connection                                                                                             | Required<br>External<br>Resistor                                                                                     | Description                                                                                                                                                                 |

|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SysClk    | ı                | See Section 19. "Clocks" on page 143.                                                                                     | When the CPU interface is configured to run with TClk instead of SysClk, SysClk is not used and must be tied to GND. | CPU interface clock. The CPU clock configuration is selected by AD[5] value at reset de-assertion. 0 = SysClk asynchronous to TClk. 1 = CPU interface is running with TClk. |

| SysRst*   | I                | See Section 20. "Reset" on page 144.                                                                                      |                                                                                                                      | The GT-64260A main reset pin. When in the reset state, all output pins (except for SDRAM address and control pins) are put into tri-state.                                  |

| TS*       | T/S I/O          | TS*                                                                                                                       | 10K-Ohm Pull-up                                                                                                      | Address tenure start                                                                                                                                                        |

| TSIZ[0:2] | T/S I/O          | TSIZ[0:2]                                                                                                                 | 10K-Ohm Pull-up                                                                                                      | Transfer size                                                                                                                                                               |

| TBST*     | T/S I/O          | TBST*                                                                                                                     | 10K-Ohm Pull-up                                                                                                      | Transfer burst                                                                                                                                                              |

| TT[0:4]   | T/S I/O          | TT[0:4]                                                                                                                   | 10K-Ohm Pull-up                                                                                                      | Transfer type                                                                                                                                                               |

| TA*       | T/S I/O          | TA*                                                                                                                       | In multi-GT mode,<br>requires 10K-Ohm<br>Pull-up.                                                                    | Transfer acknowledge                                                                                                                                                        |

| AACK*     | T/S I/O          | AACK*                                                                                                                     | In multi-GT mode,<br>requires 10K-Ohm<br>Pull-up.                                                                    | Address acknowledge                                                                                                                                                         |

| ARTRY*    | T/S I            | ARTRY*.                                                                                                                   | 10K-Ohm Pull-up                                                                                                      | Address retry.  Not sampled on the second cycle after the AACK* assertion.                                                                                                  |

| ABB*      | T/S I/O          | When working with PowerPC CPUs that use the ABB* pin as input, ABB* must be connected. Otherwise, ABB* must be pulled up. | 10K-Ohm Pull-up                                                                                                      | Address bus busy                                                                                                                                                            |

| DBB*      | T/S I/O          | When working with PowerPC CPUs that use the DBB* pin as input, DBB* must be connected. Otherwise, DBB* must be pulled up. | 10K-Ohm Pull-up                                                                                                      | Data bus is busy                                                                                                                                                            |

Table 1: CPU Interface Pin Information (Continued)

| Pin Name        | Input/<br>Output | PowerPC CPU Pin<br>Connection                                                                                                                                                                                                                    | Required<br>External<br>Resistor                                                                                                                                                                                                                                                                                                               | Description          |

|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| DTI[0-2]        | T/S O            | Only applicable on CPUs that support MPX bus. When using the MPC745x, connect to DTI[1-3] of the MPC745x. DTI[0] of the MPC745x must be pulled low. When using MPC741x, connect to DTI[0-2].                                                     | MPC740x/741x plat- forms: DTI[0]/DBWO* must be pulled up. DTI[1:2] must be pulled Low. MPC75x/PPC75x pin compatible to MPC740x/741x plat- forms: DTI[0]/DBWO* must be pulled up. DTI[1]/ARTRY* must be pulled up or con- nected to HRESET*. (See the MPC75x user manual) DTI[2] pulled down. For all other configu- rations 10K-Ohm pull-down. | Data transfer index. |

| BR0*/<br>GT_BG* | I                | When using the GT-64260A internal arbiter, connect to the primary CPU BR* pin. When using an external arbiter, connect to the arbiter GT_BG* pin.  NOTE: In single CPU systems with the internal arbiter enabled, must be used as BR0*.          | To avoid unstable states at reset, a 10K-Ohm Pull-up is recommended.                                                                                                                                                                                                                                                                           |                      |

| BG0*            | T/S O            | When using the GT-64260A internal arbiter, connect to the primary CPU BG* pin. When using an external arbiter, this pin can be left as not connected (NC).  NOTE: In single CPU systems with the internal arbiter enabled, must be used as BG0*. | To avoid unstable states at reset or when an external arbiter is used, a 10K-Ohm Pull-up is recommended.                                                                                                                                                                                                                                       |                      |

Table 1: CPU Interface Pin Information (Continued)

| Pin Name         | Input/<br>Output | PowerPC CPU Pin<br>Connection                                                                                                                                                                                                                       | Required<br>External<br>Resistor                                                                                                                                                                                                                                                                                                                                                                                                               | Description |

|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DBG0*            | T/S O            | When using the GT-64260A internal arbiter, connect the primary CPU DBG* pin. When using an external arbiter, this pin can be left as not connected (NC).  NOTE: In single CPU systems with the internal arbiter enabled, must be used as CPU DBG0*. | states at reset or when an external arbiter, is pin can be left as not concected (NC).  STE: In single CPU systems th the internal arbiter is used, a second concentration of the internal arbiter is used, a second concentration of the internal arbiter is used, a second concentration of the internal arbiter is used as CPU states at reset or when an external arbiter is used, a second concentration of the internal arbiter is used. |             |

| BR1*/<br>GT_DBG* | I                | When using single CPU systems, this pin can be left as not connected (NC). When using the GT-64260A internal arbiter, connect to the secondary CPU BR* pin. When using an external arbiter, connect to the arbiter GT_DBG* pin.                     | To avoid unstable states at reset or in a single CPU configuration, a 10K-Ohm Pull-up is recommended.                                                                                                                                                                                                                                                                                                                                          |             |

| DBG1*            | T/S O            | When using an external arbiter or single CPU systems, this pin can be left as not connected (NC). When using the GT-64260A internal arbiter, connect to the secondary CPU DBG* pin.                                                                 | To avoid unstable states at reset or when external arbiter is used, a 10K-Ohm Pull-up is recommended.                                                                                                                                                                                                                                                                                                                                          |             |

| BG1*/<br>GT_BR*  | T/S O            | When using single CPU systems, this pin can be left as not connected. When using the GT-64260A internal arbiter, connect to the secondary CPU BG* pin. When using an external arbiter, connect to the arbiter GT_BR* pin.                           | To avoid unstable states at reset or when external arbiter is used, a 10K-Ohm Pull-up is recommended.                                                                                                                                                                                                                                                                                                                                          |             |

# 3.2 60x Bus Mode

The GT-64260A can act as master and slave on the 60x bus. In this mode, the GT-64260A 60x internal arbiter supports three masters on the bus; two external 60x compatible masters, and an internal 60x master. The GT-64260A is configured to 60x bus mode by having the AD[7:6] signals sampled to b'00' at reset de-assertion. The CPU bus configuration can be read in the CPU Mode register's (Offset: 0x120) CPUType bits [7:4].

On the 60x bus, the internal 60x master supports snoop and master capability for data transfers between the GT-64260A and other agents on the 60x bus, such as another GT-64260A device.

## 3.3 MPX Bus Mode

#### Note

The GT-64260A does not support multi-GT mode in MPX bus mode.

The GT-64260A can act as master and slave on the MPX bus. In this mode, the GT-64260A 60x internal arbiter supports two masters on the bus, one external MPX compatible master and the internal CPU bus master for snoop transaction only. The GT-64260A is configured to MPX bus mode by AD[7:6] signals sampled to b'01' at reset de-assertion. The CPU bus configuration can be read in the CPU Mode Register (Offset: 0x120) bits CPU-Type (bits 7:4).

Table 2 describes the MPX bus features that are supported by the GT-64260A.

Table 2: GT-64260A Supported Features in MPX Bus Mode

| Description                                                                                                                                                                                                                                                                                                                   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| The CPU initiates a new address tenure the cycle after AACK* assertion without a dead cycle between the two address tenures.                                                                                                                                                                                                  |  |

| If the data bus is driven by the same agent in both data tenures, no dead cycle is required between two consecutive data tenures.                                                                                                                                                                                             |  |

| Load/store of AltiVec uncached operands.                                                                                                                                                                                                                                                                                      |  |

| The CPU read response data of pipelined transactions in any order. The DTI[0-2] pins indicates data tenure ID.  • 000 = data of the oldest pending read.  • 001 = the second oldest pending read.  • 010 = the third oldest pending read.  NOTE: To enable the read out of order completion, the CPU Configuration register's |  |

|                                                                                                                                                                                                                                                                                                                               |  |

# 3.4 Cache Coherency

The GT-64260A supports full cache coherency between the SDRAM and CPU caches.

Any access to the SDRAM (from PCI or IDMA) may result in a snoop transaction driven by the GT-64260A on the CPU bus. The SDRAM access to a cache coherent region is always suspended until the snoop is resolved. In case of a HIT in a modified line in CPU cache, the SDRAM access might be suspended until the line write-back to SDRAM is completed.

Figure 3 describes the transaction flow for PCI reads from cache coherent regions.

3. If there is a hit, the CPU writes the cache block to 2. The GT-64260A 60x master SDRAM (cache block snoops the transaction on the flush). Or, the snoop is CPU bus to see if the cache resolved without a CPU block is valid in the cache. **CPU** write. 4. The PCI GT-64260A receives the 1. The PCI device initailizes updated data a read transaction to cache **SDRAM** from SDRAM. coherent memory. Snoop Transaction enters to the Queue snoop queue. PCI bus

Figure 3: PCI Reads from Cache Coherent Regions

The GT-64260A supports up to four SDRAM address windows in which IDMA cache coherency is maintained. The address windows do not correlate to specific chip selects and may cross CS boundaries.

The GT-64260A also supports eight configurational address ranges (four for each PCI interface) that help maintain PCI cache coherency.

Four pairs of base/top registers define the IDMA address regions.

Table 3: IDMA Address Base/Top Registers

| Register             | Offset |

|----------------------|--------|

| Snoop Base Address 0 | 0x380  |

| Snoop Top Address 0  | 0x388  |

| Snoop Base Address 1 | 0x390  |

| Snoop Top Address 1  | 0x398  |

| Snoop Base Address 2 | 0x3A0  |

| Snoop Top Address 2  | 0x3A8  |

| Snoop Base Address 3 | 0x3B0  |

| Snoop Top Address 3  | 0x3B8  |

Each channel has a programmable bit per source, destination, and next descriptor pointer to enable/disable snoops in its Control (High) register's SrcSnoopEn, DestSnoopEn and NextSnoopEn bits. If these bits (or each one of these bits) are set, each IDMA engine transaction address is compared against the four cache coherency regions. If an address hits one of these regions, the DRAM access results in a snoop action, based on cache policy (WB/WT) as defined by the snoop regions registers Additionally, the CPU Master Control register's CleanBlock and FlushBlock bits [13:12] at offset: 0x160 must be set to the appropriate value depending on the CPU type.

The pairs of base/top registers define the PCI address regions as shown in the table below.

Table 4: PCI Address Base/Top Registers

| Register                        | PCI_0 Offset | PCI_1 Offset |

|---------------------------------|--------------|--------------|

| PCI Snoop Control Base 0 (Low)  | 0x1F00       | 0x1F80       |

| PCI Snoop Control Base 0 (High) | 0x1F04       | 0x1F84       |

| PCI Snoop Control Top 0         | 0x1F08       | 0x1F88       |

| PCI Snoop Control Base 1 (Low)  | 0x1F10       | 0x1F90       |

| PCI Snoop Control Base 1 (High) | 0x1F14       | 0x1F94       |

| PCI Snoop Control Top 1         | 0x1F18       | 0x1F98       |

| PCI Snoop Control Base 2 (Low)  | 0x1F20       | 0x1FA0       |

| PCI Snoop Control Base 2 (High) | 0x1F24       | 0x1FA4       |

| PCI Snoop Control Top 2         | 0x1F28       | 0x1FA8       |

| PCI Snoop Control Base 3 (Low)  | 0x1F30       | 0x1FB0       |

| PCI Snoop Control Base 3 (High) | 0x1F34       | 0x1FB4       |

| PCI Snoop Control Top 3         | 0x1F38       | 0x1FB8       |

Each PCI transaction address is compared against the four cache coherency regions. If an address hits one of these regions, the DRAM access results in a snoop action, based on cache policy (WB/WT) and as defined by the snoop region registers. Additionally, the CPU Master Control registers CleanBlock and FlushBlock bits [13:12] at offset 0x160 must be set to the appropriate value depending on the CPU type.

# 3.4.1 Cache Coherency Initialization Sequence

The cache coherency initialization sequence is as follows:

- 1. The CPU Configuration register's AACK Delay bit [11], at offset 0x000, must be set to '1'. See the latest GT-64260A errata and restrictions document for more information.

- In the CPU Master Control at offset 0x160, set the CleanBlock and FlushBlock bits [13:12] to the correct value, depending on the CPU type. See the GT-64260A datasheet's "CPU Interface" section for more information.

- 3. Configure cache coherent windows for the desired interface with the PCI cache coherency registers (0x1F00 0x1F38) and the IDMA cache coherency registers (0x380 0x3B8).

- 4. Confirm that the Snoop Control Base (Low) register's Snoop bits [13:12] at offset 0x1F00–0x1F30 are set to the correct value, depends on the CPU cache policy (WB or WT).

NOTE: The cache coherency will not be enabled when these bits are set to No snoop (0x0).

5. When using the PCI access control registers (base smaller than top) 0x1E00 - 0x1E78, the MBurst bits to the cache coherent memory must be set to 0x0 (four 64-bit words).

**NOTE:** Never configure the communication interface to work with cache coherent regions (see GT-64260A errata and restriction document).

It is the designer's responsibility to ensure that the CPU is configured correctly to support the cache coherency. For example, make sure that the W, I, M, G bits in the block attributes or page table entry indicate the correct setting of the processor cache policy.

# 3.5 Specific CPUs Aspects

### 3.5.1 MPC745x Burst to Boot Address

The MPC745x instruction queue holds as many as 12 instructions and loads as many as four instructions per cycle. After reset the MPC745x fetches instructions from the boot device (or any other cache-inhibited memory), in 60x-bus mode, the bus access is a 32 byte transaction (even though only the required 16 bytes are transmitted to the instruction queue). In MPX bus mode, a cache-inhibited instruction fetch performs a 16 byte transaction on the bus.

Since the MPC745x's first transaction after boot is 32/16 byte read and the GT-64260A does not support burst longer than 8 byte from 8-bits or 16-bits wide devices, implement one of the following solutions.

- Use 32-bit wide boot device.

- Use the Serial ROM Initialization at reset to copy 8-bit flash device to another 32-bit device (e.g. SRAM).

For example, the GT-64260A with the MPC745x evaluation platform (EV-64260ABP-MPC7450) uses an 8-bit wide flash device and a 32-bits wide SRAM device to boot the CPU. Before the CPU reset de-assertion, the 8-bit flash is copied to the 32-bits SRAM device by the I2C interface

#### Note

For more information on the serial ROM initialization, see the GT-64260A datasheet's "Reset Configuration" section.

### **System Initialization Sequence**

The system initialization sequence is as follows:

- 1. On the device bus, implement one 8-bit flash memory (used as the boot device connected to one of the CS\* signals) and a 32-bit wide SRAM on the boot chip select (BootCS\*).

- Treat the 8-bit flash memory as the boot device. This means the boot image must be burned in the flash memory.

- 3. Burn an I<sup>2</sup>C EEPROM with a data sequence that initiates a DMA transfer from the 8-bit boot device to the 32-bit SRAM. See Appendix A. "I2C EEPROM Example" on page 147.

- 4. Configure the GT-64260A to serial ROM initialization enabled (AD[0] set to '1').

#### Note

When booting from an  $I^2C$  EEPROM, the CPU must be kept at reset as long as the initialization process takes place. This is accomplished by using the InitAck pin, driven by the GT-64260A during the initialization, on one of the MPP pins. The MPP pin that functions as InitAck pin must be pulled high and configured to function as InitAct at the  $I^2C$  EEPROM file.

If this procedure is correctly executed, the PPC745x boots from the 32-bit SRAM, instead of from the 8-bit flash device.

Copyright © 2002 Marvell CONFIDENTIAL Doc. No. MV-S300165-00, Rev. A

#### Note

Make sure that all the Reset configuration strapping required by the GT-64260A with serial ROM initialization are pulled to the correct values (the same value configured in the serial initialization). For more information, see the GT-64260A datasheet's "Reset Configuration" section.

# 3.5.2 MPC7410, MPC745x and PPC750CX/e Bus Voltage

The MPC7410, MPC745x and PPC750CX/e only supports 1.8V and 2.5V bus voltages (except for the 3.3V version of the MPC7410). Alternatively, the GT-64260A supports 2.5V and 3.3V CPU interface voltages.

Therefore, when using one of these CPUs, it must be configured to work in 2.5V on the CPU bus by configuring the CPU's BVSEL pin to the correct value at reset. In addition, the GT-64260A's CPU interface must be configured to 2.5V at reset by setting AD31 to '0'.

#### Note

AD31 must be pulled to the correct value at reset even when the serial ROM is enabled. This means the CPU interface voltage value (AD[31]) and the serial initialization value (AD[0]) must be the same.

### 3.5.3 MPC745x Extended Pins

The MPC745x CPU supports a 32-bit addressing mode and a 36-bit extended addressing modes. When extended physical addressing is disabled, the MPC745x drives the four most significant bits to zeroes.

#### Note

The four most significant bits are still sampled and must be actively pulled to zero if they are not being used in a system.

The MPC745x Address and address parity buses must be connected to the GT-64260A as follows:

- Pull MPC745x A[0:3] to b'0000'.

- Connect MPC745x A[4:35] to GT-64260A A[0:31].

- Pull MPC745x AP[0] to b'1'.

- Connect MPC745x AP[1:4] to GT-64260A AP[0:3].

Additionally, the MPC745x microprocessor supports a 4-bit DTI index, with a maximum value of DTI[0:3] = b'1111'. Therefore, the DTI bus must be connected to the GT-64260A as follows:

- Pull MPC745x DTI[0] to b'0'.

- Connect MPC745x DTI[1:3] to GT-64260A DTI[0:2].

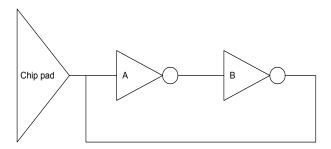

### 3.5.4 PPC750FX Level Protection

The PPC750FX CPU implements signal 'keepers' on some of its IO pads. The keeper can be viewed as two cross-coupled inverters. (See Figure 4). Inverter B is extremely weak. It can supply a maximum of ~50uA.

Figure 4: PPC750FX CPU Keeper

Since the 'keepers' are not biased to drive the IOs one way or the other, any control signals that must be in a particular state leaving HRESET\* have to be either driven to that state or pulled there by external resistors.

The designer can connect two 'keepers' on the same signals (i.e. multiple PPC750FX systems), since they will always drive the same value. Theoretically, two keepers can end up in contention during power up. However, since this would be unstable, any noise event would knock it to a '1' or '0'.

The bus keeper can supply up to ~50uA. This means if there is a Pull-up (e.g., 10K-Ohm) and the last value was Low ('0'), the Pull-up will start pulling the signal high but the maximum current is 50 uA =>.

V(signal) = V(io) - [R(pull up) \* I(maximum)] = 2.5 - [10000 \* 0.00005]

V(signal) = 2V.

#### Note

IBM recommends using a 5K Ohm Pull-up that pulls the signal to 2.25V.

When the signal reaches the 'keeper' threshold voltage, the keeper drives the signals high and the signal voltage reaches the V(IO) value.

A similar calculation can be used for the pull down with keeper. In this case with 10K Ohm V(signal) = 0.5V (or 0.25V for 5K Ohm). When the signal reaches to the 'keeper' threshold voltage, the keeper starts driving the signals low and the signal voltage reaches the GND value.

#### Note

For more information, see the IBM datasheet.

# 3.5.5 PPC750FX Data Bus Parking

The GT-64260A internal 60x arbiter supports data bus parking.

See the GT-64260A errata and restriction document errata "FEr #CPU-1 Multiple data bus masters with IBM PPC750CX/e CPUs". This errata is also applicable to PPC750FX DD1.x Revisions. The dd2.0 Revision and higher will support data bus parking.

### Note

PPC750FX first production revision is DD2.1. It is the revision that supports the data bus parking. Previous revisions are defined as prototypes.

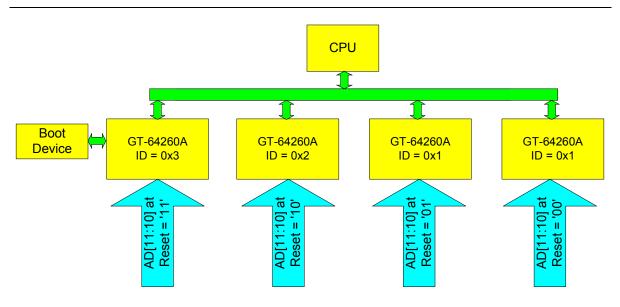

# 3.6 Multi-GT or Multi-slave Modes

It is possible to connect up to four GT-64260A or other 60x-bus compliant slave devices to the 60x bus without the need for any glue logic. This capability (referred to as "Multi-GT" mode) adds significant system design flexibility. Multiple GT-64260A is enabled by setting AD[9] to '1' at reset.

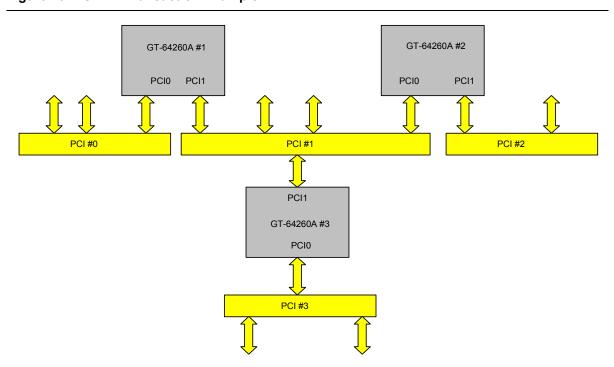

Figure 5 describes the Multi-GT system architecture.

### Note

Each GT-64260A in the figure can be removed or replaced by another 60x compatible slave.

Figure 5: Multi-GT System Architecture

#### Note

In multi-GT configuration, the AACK\* and TA\* pins function as sustained tri-state outputs requiring Pull-up resistors (see Table 1, "CPU Interface Pin Information," on page 14). All TA\* outputs from the GT-64260A devices must be tied together to drive the CPU TA\* input. All AACK\* outputs from the GT-64260A devices must be tied together to drive the CPU AACK\* input.

When multi-GT is enabled, after reset de-assertion the GT-64260A uses a reduced address-decoding scheme as long as the CPU Configuration register's MultiGTDec bit [18], at offset 0x000, is set to '1'. In this mode, each GT-64260A device has a two bit ID that is sampled at reset on AD[11:10] pins. Each device responds to the transaction address that matches its ID, as shown in Table 5:

Table 5: Multi-GT Device ID

| ID | Multi-GT Address ID |

|----|---------------------|

| 00 | A[5-6] = 00         |

| 01 | A[5-6] = 01         |

| 10 | A[5-6] = 10         |

| 11 | A[5-6] = 11         |

### Note

The boot GT-64260A ID must be programmed to '11'.

The GT-64260A translates the CPU transactions as shown in Table 6.

Table 6: Multi-GT Mode Transaction Translation

| AD[4]            | Transaction Type | Transaction Decode                                                               |

|------------------|------------------|----------------------------------------------------------------------------------|

| ,0,              | READ             | Read from internal register when A[20-31] defining the specific register offset. |

| <b>'1'</b>       | READ             | Read access from boot device (BootCS*).                                          |

| 'x' (don't care) | WRITE            | Write to internal register when A[20-31] defining the specific register offset.  |

For example, the boot GT-64260A (ID='11') responds to a read transaction from address 0xFFF00100. This transaction is translated to a read from the boot device at offset 0x100. A write transaction to address 0x00000000 gets a response from the GT-64260A configured as ID='00'. This transaction is translated to a write to its internal register offset at 0x000.

For more information on the multi-GT initialization sequence and system considerations see the following:

- The GT-64260A datasheet's "CPU Interface" section

- AN-91 Multi-GT Mode in the GT-6426xx

#### **Notes**

- When multi-GT is enabled at reset, the NoMatch counter is only applicable to the GT-64260A boot.

- In multi-GT mode AACK\* and TA\* pins have different AC timings. For details, see the GT-64260A datasheet's "AC Timing" section and the GT-64260A Documentation Updates and Changes document.

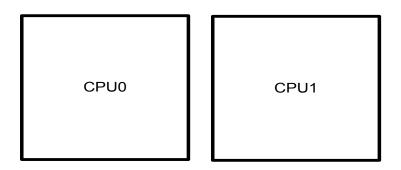

# 3.7 CPU Bus Multiple Masters

The PowerPC bus protocol supports separate arbitration on address and data busses. The arbitration must be implemented to support multiple masters on the CPU bus. The "multiple masters" configuration is usually used in a Symmetric Multiple Processing (SMP) system. For an SMP system to be fully functional, it requires additional HW implementations.

### 3.7.1 PowerPC Bus Arbitration