# TRF6151 RITA Quadruple band GSM Single chip Transceiver

# **Specification**

**RIT000**

**Vers 3.0**

File: RITA Specification.pdf

Department: WTBU Chipset 2G - 2.5G

|           | Originator                     | Approval                                                 | Quality |

|-----------|--------------------------------|----------------------------------------------------------|---------|

| Name      | Pascal AUDINOT<br>Jerome DEMAY | Marc COUVRAT Pascal LEMASSON Eric DUVIVIER Pierre CARBOU |         |

| Date      | 12/4/02                        |                                                          |         |

| Signature |                                |                                                          |         |

TI - Proprietary Information -

Page 1 of 71

#### **HISTORY**

| Version  | Date     | Author         | Notes          |

|----------|----------|----------------|----------------|

| Vers 1.0 | 12/20/01 | Estelle PROUX  | First version  |

|          |          | Francois BELIN |                |

|          |          | Angel EZQUERRA |                |

|          |          | Jerome DEMAY   |                |

| Vers 2.0 | 03/28/02 | Estelle PROUX  | Second version |

|          |          | Francois BELIN |                |

|          |          | Angel EZQUERRA |                |

|          |          | Jerome DEMAY   |                |

| Vers 2.1 | 04/04/02 | Jerome DEMAY   | Third version  |

| Vers 2.2 | 05/02/02 | Francois BELIN | Fourth version |

|          |          | Jerome DEMAY   |                |

| Vers 2.3 | 05/30/02 | Jerome DEMAY   | Fifth version  |

| Vers 3.0 | 12/03/02 | Estelle PROUX  | Sixth version  |

|          |          | Jerome DEMAY   |                |

#### **NOTES:**

- 1.0 Creation

- 2.0 Update following Designers'inputs PA controller specification added

- 2.1 VCC pin swap

- 2.2 P.A.U.C. specification added

- 2.3 Current consumption table updated

- 3.0 Global Input 1dB blocking compression point table added Update of serial interface P.A.U.C. specification removed

TI - Proprietary Information -

**Page 2 of 71**

**Strictly Private**

#### **TABLE OF CONTENT**

| Introduction                                          | 5  |

|-------------------------------------------------------|----|

| References                                            | 7  |

| Chipset block diagram                                 |    |

| Application Board Functional Block Diagram            | 9  |

| Terminal diagram                                      | 10 |

| Pins description                                      | 11 |

| Package characteristics                               | 13 |

| Absolute Maximum Ratings                              | 15 |

| Recommended Operating Conditions                      | 15 |

| Electrical Characteristics                            |    |

| Current Consumption                                   | 16 |

| OFF mode                                              |    |

| Receive mode                                          | 16 |

| Transmit mode                                         | 16 |

| RX ON in High gain                                    | 17 |

| TX ON                                                 |    |

| Voltage regulation                                    | 19 |

| Band gap                                              |    |

| Regulator R1                                          |    |

| Regulator R2                                          |    |

| Regulator R3                                          |    |

| Regulators power domains                              |    |

| Temperature sensor                                    |    |

| Synthesizer                                           |    |

| Crystal and External Varactor network                 |    |

| Reference clock input                                 |    |

| VCXO buffer output (XOUT pin)                         |    |

| Main synthesizer in RX mode for GSM 850 and E-GSM 900 |    |

| Main synthesizer in RX mode for DCS 1800 and PCS 1900 |    |

| Main synthesizer in TX mode for GSM 850 and E-GSM 900 |    |

| Main synthesizer in TX mode for DSC 1800 and PCS 1900 | 28 |

| Synthesizer Power up / down time                      |    |

| Transmitter                                           |    |

| Transmitter inputs                                    |    |

| Low Band Output                                       |    |

| Low Band Output (continued)                           | 30 |

| High Band Output                                      | 31 |

| High Band Output (continued)                          |    |

| Modulated output spectrum                             |    |

| Spurious emissions                                    |    |

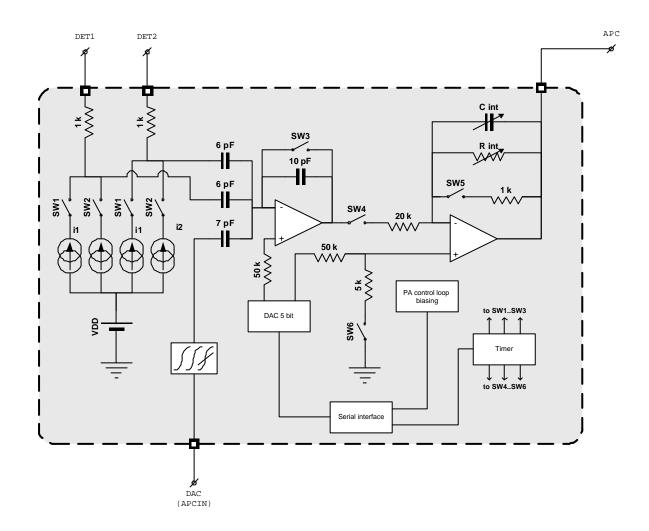

| Power Amplifier Controller                            |    |

| Low pass filter for DAC signal (1st order)            |    |

| Sense amplifier                                       |    |

| Integrator                                            |    |

| Current generators                                    |    |

| Home position voltage                                 |    |

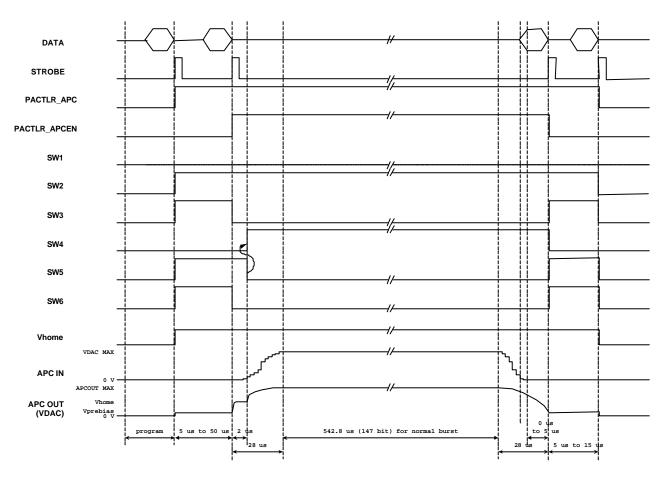

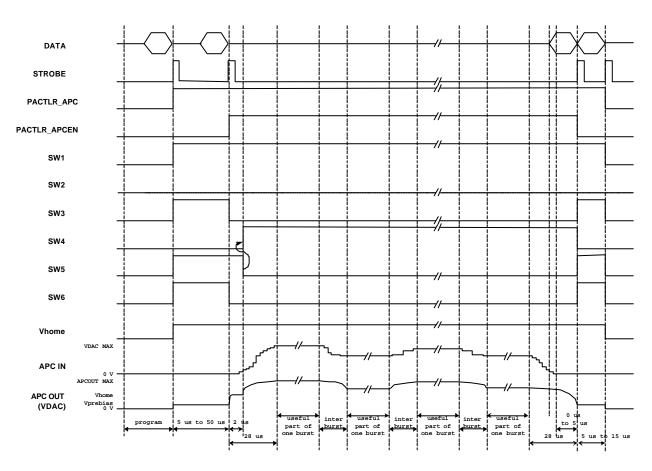

| Power up/down time                                    |    |

| Receiver                                              |    |

| Global performances.                                  |    |

|                                                       |    |

TI – Proprietary Information –

**Page 3 of 71**

| Global performances (continued)                               | 40 |

|---------------------------------------------------------------|----|

| Global performances (continued)                               | 41 |

| Low band GSM850-GSM900 LNA (LNAGSM) + IQ demodulator (MIXGSM) | 43 |

| DCS LNA (LNADCS) + IQ demodulator(MIXDCS)                     | 44 |

| PCS LNA (LNAPCS) + IQ demodulator (MIXPCS)                    | 45 |

| Post IQ demodulator low pass filter                           | 46 |

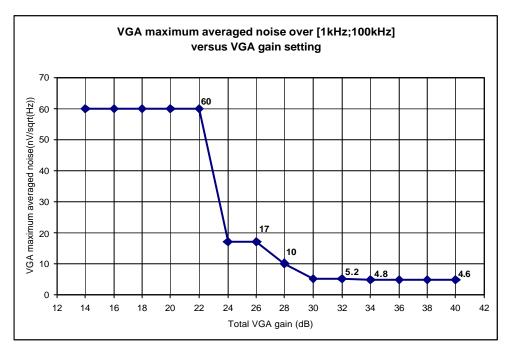

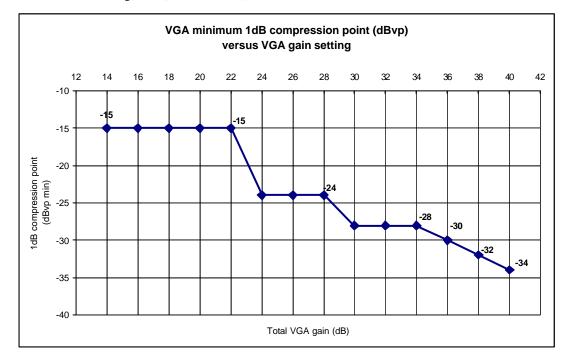

| Base band amplifier (VGA)                                     | 46 |

| Global characteristics                                        | 46 |

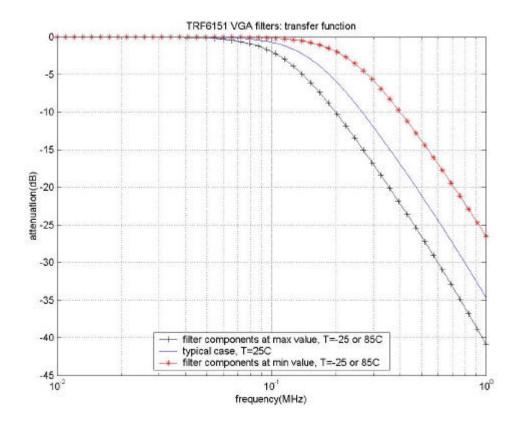

| VGA filters                                                   | 48 |

| DC offset compensation system                                 | 48 |

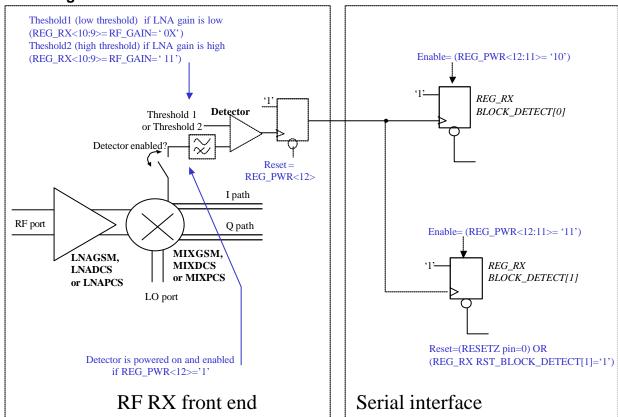

| Interferer detection system                                   | 49 |

| Receiver Power up / down time                                 | 49 |

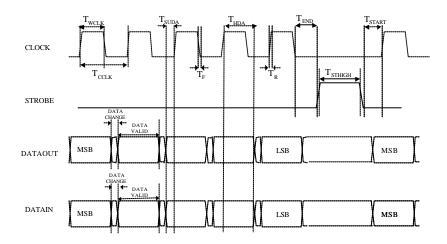

| Serial data interface description                             | 50 |

| Serial interface timing                                       |    |

| Serial interface programming                                  | 51 |

| Serial word format                                            | 51 |

| Registers table                                               | 51 |

| REG_RX register                                               |    |

| REG_PLL register                                              | 53 |

| REG_PWR register                                              |    |

| REG_CFG register                                              | 55 |

| Annex 1: PLL_mode                                             |    |

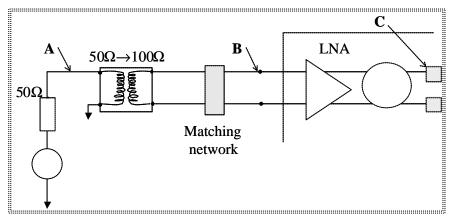

| Annex 2: Front End measurement schematic                      |    |

| Annex 3: TRF6151 receiver configurations                      |    |

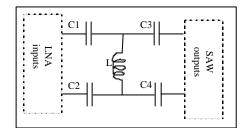

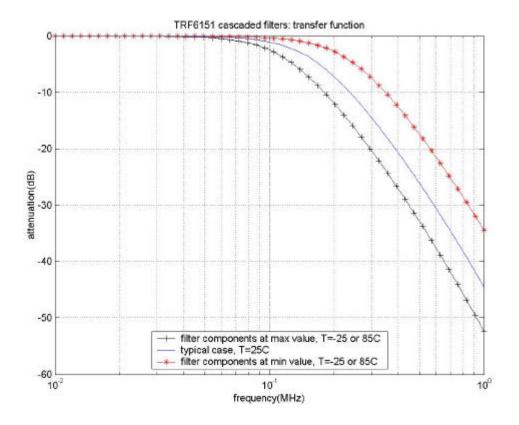

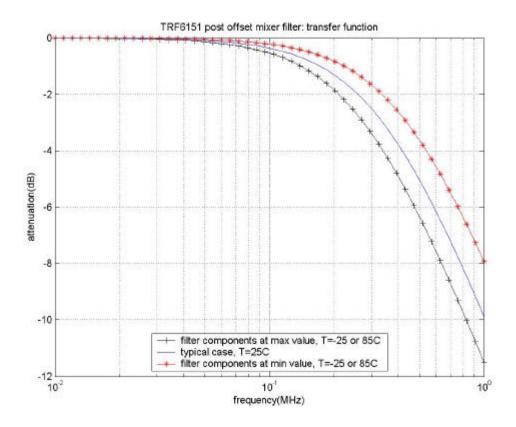

| Annex 4: TRF6151 filters                                      |    |

| Annex 5: Input 1dB blocking compression point table           |    |

| Annex 6: Reference clock connection.                          |    |

| Annex 7: Interferer detection system                          |    |

| Principle                                                     |    |

| Block diagram                                                 |    |

| Detection process                                             |    |

| Annex 8: Test procedure for RX lock time                      |    |

| Test #1: locking time from "OFF" to "RX" state                |    |

| Test #2: locking time from "RX GSM" to "RX DCS" state         | 71 |

TI – Proprietary Information –

Page 4 of 71

#### **INTRODUCTION**

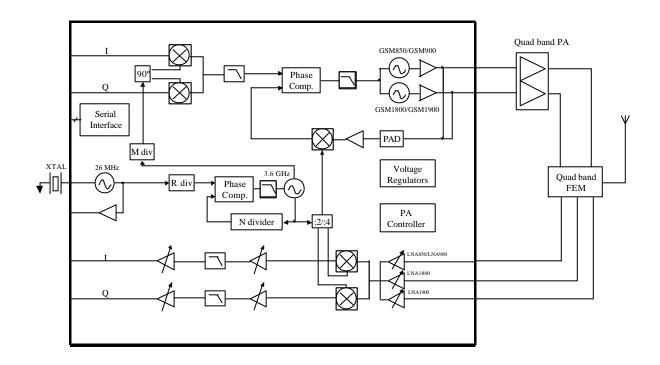

The TRF6151 is a quadruple band transceiver IC suitable for GSM 850, GSM 900, DCS 1800 and PCS 1900 GPRS class 12 applications. The chip integrates the receiver based on direct conversion architecture, the transmitter based on the modulation loop architecture, the frequency synthesis including a 26MHz VCXO, a MAIN N-integer synthesizer, 2 MAIN VCOs, a programmable MAIN loop filter, 2 TX VCOs, a TX loop filter, the voltage regulators to supply on chip and off chip RF functions and a power amplifier controller.

Few external components are required for a "quad band" application as a power amplifier and a front-end module.

It is housed in a 48 pins 7x7mm - 0.5mm pitch QFN package.

The TRF6151 transceiver is part of TI GSM chipset. It is compatible with Iota (TWL3014) and Syren (TWL3016) ABB chips and with Calypso, Calypso20G2, Calypso-plus and Perseus2 DBB chips.

The chip combines the following functions:

#### 1. Transmit section:

- an offset PLL with post IQ modulator and post offset mixer filters fully integrated on chip

- two TX VCOs fully integrated on chip

- a TX loop filter fully integrated on chip

- a divider by 4 for the LO generation in GSM900 and GSM850

- a divider by 2 for the LO generation in DCS1800 and PCS1900

- a programmable M divider for the IF generation

- a power amplifier controller including all the functions required to design a power sensing control loop except the sensing diodes

TI - Proprietary Information -

**Page 5 of 71**

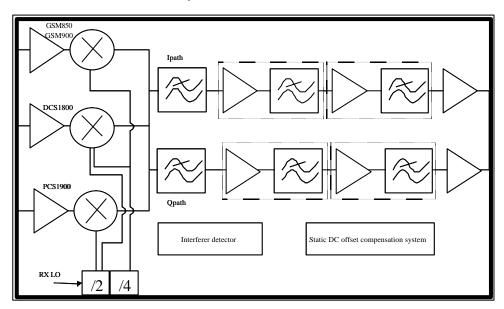

#### 2. Receive section:

- a GSM900/GSM850 LNA (LNAGSM) with switchable gain

- a DCS1800 LNA (LNADCS) with switchable gain

- a PCS1900 LNA (LNAPCS) with switchable gain

- three quadrature demodulators for GSM900/GSM850 (MIXGSM), DCS1800 (MIXDCS) and PCS1900 (MIXPCS) bands with switchable gain

- two base-band amplifiers with digitally programmable gain

- two fully integrated base-band channel filters.

- two DC offset compensation systems

- a divider by 4 for the LO generation in GSM900 and GSM850 in order to minimize the DC offset generated by self mixing and the LO re-radiation

- a divider by 2 for the LO generation in DCS1800 and PCS1900 in order to minimize the DC offset generated by self-mixing and the LO re-radiation.

- an interferer detection system

Figure 1 - Receiver block diagram

#### 3. Common to both sections:

- a 26MHz VCXO with external varactor and crystal

- a 26 MHz buffer to drive the DBB

- two MAIN VCOs fully integrated on chip

- a MAIN N-integer synthesizer

- a programmable MAIN loop filter fully integrated on chip

- 3 voltage regulators to supply internal functions and external RF components

- a digital serial interface

#### **REFERENCES**

- [1] 3GPP TS05.05 version 8.10

- "Digital cellular telecommunications system (phase 2+); Radio transmission and reception "

- [2] 3GPP TS51.010-1 version 4.4.0

- "Digital cellular telecommunications system (phase 2+); MS conformance specification "

- [3] TWL3014 v1.2 specification (Iota) Internal document Texas Instruments

- [4] Time serial port specification HYP004 v1.0 Internal document Texas instruments

TI - Proprietary Information -

Page 7 of 71

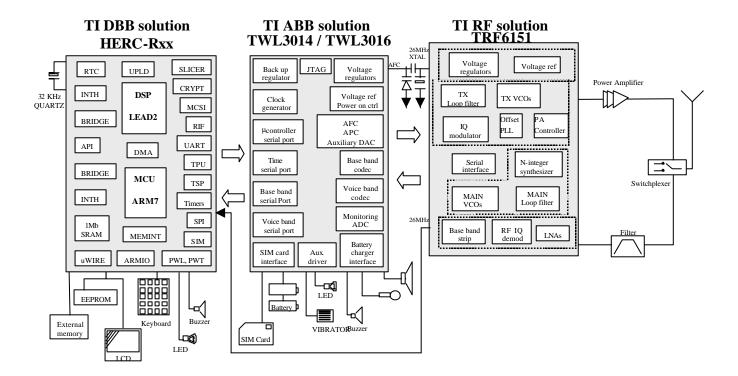

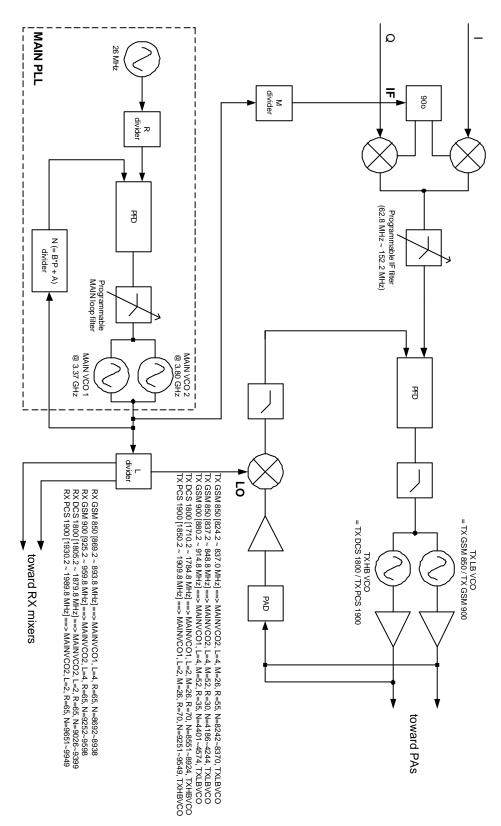

#### CHIPSET BLOCK DIAGRAM

# **TI chipset = HERCRxx + TWL3014 / TWL3016 + TRF6151**

Figure 2 - Chipset block diagram

TI - Proprietary Information -

Page 8 of 71

**Strictly Private**

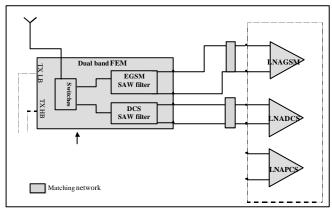

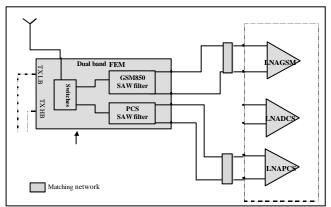

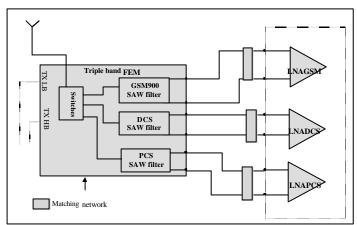

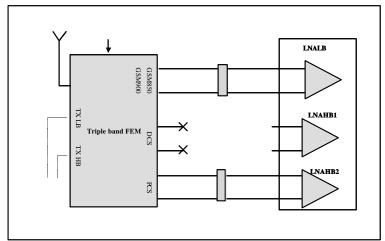

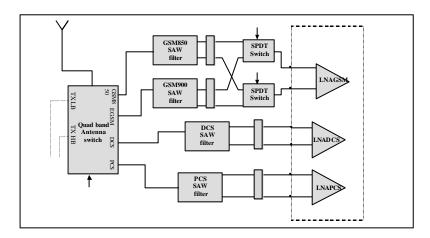

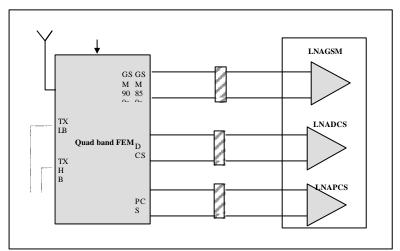

#### APPLICATION BOARD FUNCTIONAL BLOCK DIAGRAM

Figure 3 - TRF6151 block diagram

TI - Proprietary Information -

Page 9 of 71

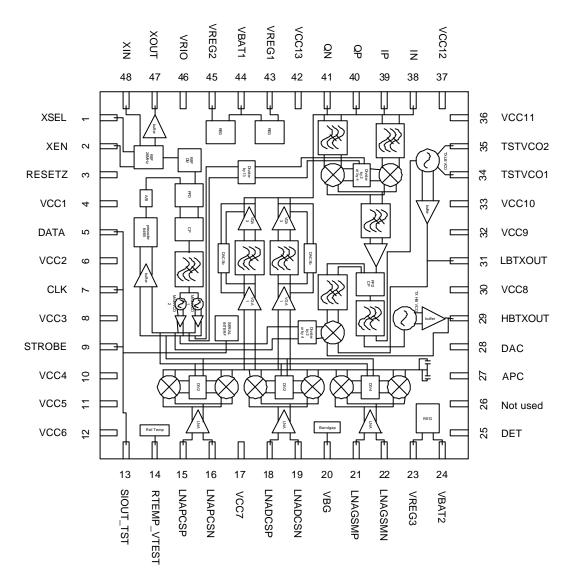

#### **TERMINAL DIAGRAM**

Figure 4 - TRF6151 terminal diagram (top view)

TI - Proprietary Information -

Page 10 of 71

**Strictly Private**

#### PINS DESCRIPTION

| PIN NAME    | PIN# | I/O | DESCRIPTION                                                  |

|-------------|------|-----|--------------------------------------------------------------|

| XSEL        | 1    | I   | Xtal select external or internal                             |

| XEN         | 2    | I   | Xtal enable (VCXO and buffer supply)                         |

| RESETZ      | 3    | I   | Serial interface reset input                                 |

| VCC1        | 4    | VCC | PLL supply voltage                                           |

| DATA        | 5    | I   | Serial interface data input                                  |

| VCC2        | 6    | VCC | PLL supply voltage                                           |

| CLK         | 7    | I   | Serial interface clock input                                 |

| VCC3        | 8    | VCC | PLL supply voltage                                           |

| STROBE      | 9    | I   | Serial interface strobe input                                |

| VCC4        | 10   | VCC | MAIN VCO2 supply voltage (2.0Volts internally generated)     |

| VCC5        | 11   |     | VCO DIVIDER supply voltage                                   |

| VCC6        | 12   | VCC | MAIN VCO1 supply voltage (2.0Volts internally generated)     |

| SIOUT_TST   | 13   | 0   | Serial interface output multiplexed with PLL test            |

| RTEMP_VTEST | 14   | О   | Temperature sensor output and VCO test                       |

| LNAPCSP     | 15   | I   | RX PCS LNA input (+)                                         |

| LNAPCSN     | 16   | I   | RX PCS LNA input (-)                                         |

| VCC7        | 17   | VCC | RX LNA supply voltage                                        |

| LNADCSP     | 18   | I   | RX DCS LNA input                                             |

| LNADCSN     | 19   | I   | RX DCS LNA input                                             |

| VBG         | 20   | О   | Bandgap voltage output                                       |

| LNAGSMP     | 21   | I   | RX GSM LNA input (+)                                         |

| LNAGSMN     | 22   | I   | RX GSM LNA input (-)                                         |

| VREG3       | 23   | О   | Regulator 3 output dedicated to VCC8, VCC10                  |

| VBAT2       | 24   | I   | Regulator 3 battery voltage supply                           |

| DET         | 25   | I   | PA controller DETECT input                                   |

| Not used    | 26   | -   | Not used                                                     |

| APC         | 27   | О   | PA controller output                                         |

| DAC         | 28   | I   | PA controller APC input                                      |

| HBTXOUT     | 29   | 0   | TX DCS/PCS output                                            |

| VCC8        | 30   | VCC | TX VCO buffer supply voltage (2.7V)                          |

| LBTXOUT     | 31   |     | TX GSM900 / GSM850 output                                    |

| VCC9        | 32   | VCC | TX HB VCO core supply voltage (2.4V internally generated)    |

| VCC10       | 33   | VCC | TX VCO and RX mixer supply voltage                           |

| TSTVCO1     | 34   | I/O | LB TX VCO test (tank if Pnoise spec not reached)             |

| TSTVCO2     | 35   | I/O | LB TX VCO test (tank if Pnoise spec not reached)             |

| VCC11       | 36   | VCC | TX LB VCO core supply voltage (2.4V internally generated)    |

| VCC12       | 37   | VCC | IQ modulator supply voltage and RX VGA supply voltage (2.7V) |

| IN          | 38   | I/O | In phase baseband I/O (-)                                    |

| IP          | 39   | I/O | In phase baseband I/O (+)                                    |

| QP          | 40   | I/O | Quadrature phase baseband I/O (+)                            |

| QN          | 41   | I/O | Quadrature phase baseband I/O (-)                            |

| VCC13       | 42   | VCC | TX charge pump supply voltage (2.7V)                         |

| VREG1       | 43   | O   | Regulator 1 output dedicated to VCC7, VCC12, VCC13           |

| VBAT1       | 44   | I   | Regulator 1 and regulator 2 battery voltage supply           |

TI – Proprietary Information –

Page 11 of 71

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

UNDER NON DISCLOSURE AGREEMENT

DO NOT COPY

| VREG2 | 45 | О   | Regulator 2 output dedicated to VCC1, VCC2, VCC3, VCC5 |

|-------|----|-----|--------------------------------------------------------|

| VRIO  | 46 | VCC | Serial interface supply voltage                        |

| XOUT  | 47 | 0   | Xtal buffer output                                     |

| XIN   | 48 | I   | Xtal input                                             |

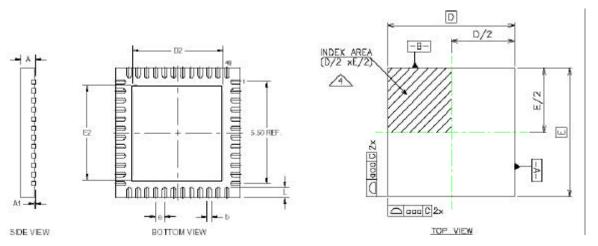

#### PACKAGE CHARACTERISTICS

48 pins QFN 7x7mm – 0.5mm pitch

**Figure 5 - Component Dimensions**

#### BODY SIZE = $7.0 \times 7.0 \text{mm}$ , THICKNESS = 0.9 mm

| SYMBOL | Package Dimensions with Tolerance |          |      |  |

|--------|-----------------------------------|----------|------|--|

|        | MIN.                              | NOM.     | MAX. |  |

| A      | =                                 | 0.85     | 0.90 |  |

| A1     | 0                                 | 0.02     | 0.05 |  |

| D      | 6.85                              | 7.00     | 7.15 |  |

| D2     | 5.00                              | 5.15     | 5.25 |  |

| E      | 6.85                              | 7.00     | 7.15 |  |

| E2     | 5.00                              | 5.15     | 5.25 |  |

| L      | 0.30                              | 0.40     | 0.50 |  |

| b      | 0.18                              | 0.23     | 0.30 |  |

| e      | -                                 | 0.50 BSC | -    |  |

All dimensions in Millimeters

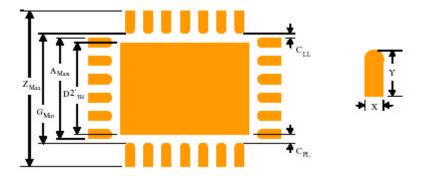

**Figure 6 - PCB Land Pattern Dimensions**

|        | Board Land Pattern Dimensions |      |      |      |      |                   |

|--------|-------------------------------|------|------|------|------|-------------------|

| SYMBOL | Zmax                          | Amax | Gmin | Xmax | Yref | D2' <sub>TH</sub> |

|        | 7.36                          | 5.78 | 5.98 | 0.28 | 0.69 | 5.68              |

All dimensions in Millimeters

Note: Xmax dimension reduced to avoid solder bridging

TI - Proprietary Information -

Page 13 of 71

**Strictly Private**

#### **TBD**

Figure 7 - Thermal Pad Stencil Design

More information on Package Characteristics is available on: http://www1.itg.ti.com/msp\_packaging/docs/qfn/qfn\_home.htm, "Available QFN Package Information"

#### ABSOLUTE MAXIMUM RATINGS

# **Absolute Maximum Ratings Over Operating Free-Air Temperature Range** (Unless Otherwise Noted)

| Chip supply voltage range: VBAT                               | 0.3 V to 5.5 V |

|---------------------------------------------------------------|----------------|

| Input voltage to any other pin:                               | tbd V          |

| Power dissipation, Ta = 25 °C, 48 Pin QFN 7x7mm - 0.5mm pitch | tbd mW         |

| Storage temperature range                                     | 65 to +150 °C  |

| ESD integrity <sup>1</sup>                                    | tbd HBM        |

#### RECOMMENDED OPERATING CONDITIONS

|                                | MIN       | TYP | MAX         | UNIT |

|--------------------------------|-----------|-----|-------------|------|

| VRIO Supply voltage            | 2.7       | 2.8 | 2.9         | V    |

| VIH High level input voltage   | 0.8*VRIO  |     |             | V    |

| VIL Low level input voltage    |           |     | 0.22 x VRIO | V    |

| VOH High level output voltage  | 0.7*VRIO  |     | VRIO+0.5    |      |

| VOL Low level output voltage   | -0.5      |     | 0.3*VRIO    |      |

| VCC Supply voltage             | 2.7       | 2.8 | 2.9         | V    |

| VBAT Supply voltage            | $3.0^{2}$ | 3.6 | 5.5         | V    |

| Ta Operating Temperature range | -25       |     | +85         | °C   |

<sup>&</sup>lt;sup>2</sup> 3.0 V corresponds to VBATMIN ==> When MS is emitting at full power, the battery voltage must never be under 3.0 V at Rita regulators inputs

TI - Proprietary Information -

Page 15 of 71

**Strictly Private**

<sup>&</sup>lt;sup>1</sup> Sensitive RF pins (LNA inputs, TXVCO outputs) are not protected against voltage stress higher than 300 V HBM (tbc).

#### **ELECTRICAL CHARACTERISTICS**

Typical: Vcc = 2.8 V,  $Ta = +25^{\circ}\text{C}$ Max. and Min.:  $Ta = -25^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$

# **CURRENT CONSUMPTION<sup>3</sup>**

| Power mode                       | Test conditions                                                                  | Band | Typical operating |

|----------------------------------|----------------------------------------------------------------------------------|------|-------------------|

|                                  |                                                                                  |      | current           |

| OFF mode                         |                                                                                  |      |                   |

| ALL OFF                          | All functional blocks powered OFF                                                | -    | 5 uA              |

| ALL OFF except BG                | Band gap ON and all<br>others functional blocks<br>powered OFF                   | -    | 80 uA             |

| ALL OFF except BG and Regulators | Band gap and<br>Regulators ON and all<br>others functional blocks<br>powered OFF | -    | 0.6 mA            |

#### Receive mode

| RX synthesizer ON          | Main PLL is locking     | GSM850 / GSM900 | 8.0 mA  |

|----------------------------|-------------------------|-----------------|---------|

|                            |                         | DCS1800         | 8.0 mA  |

|                            |                         | PCS1900         | 8.0 mA  |

| RX synthesizer ON + DC     | Main PLL and RX         | GSM850 / GSM900 | 44.0 mA |

| offset calibration running | calibration process are | DCS1800         | 46.0 mA |

|                            | ON                      | PCS1900         | 46.0 mA |

| RX ON in High gain         | Main PLL, LO            | GSM850 / GSM900 | 53.0 mA |

|                            | generation, LNA, IQ     | DCS1800         | 55.0 mA |

|                            | demodulator and         | PCS1900         | 55.0 mA |

|                            | Baseband strip are ON   |                 |         |

#### Transmit mode<sup>4</sup>

| Main TX synthesizer ON | controller ON and PA controller    | Low Band  | 11.0 mA  |

|------------------------|------------------------------------|-----------|----------|

| + PA controller ON     |                                    | High Band | 11.0 mA  |

| TX ON                  | Main PLL and Offset                | Low Band  | 116.0 mA |

|                        | PLL, LO/IF generation, IQ          | High Band | 106.0 mA |

|                        | modulator and PA controller are ON |           |          |

<sup>&</sup>lt;sup>4</sup> with P.A.U.C. the typical current consumption is 2.0 mA higher

TI - Proprietary Information -

Page 16 of 71

<sup>&</sup>lt;sup>3</sup> VCXO (supplied by an external voltage source) typical current consumption is 1.1 mA

| Module | VCC line | Band | Typical operating |

|--------|----------|------|-------------------|

|        |          |      | current           |

#### **RX ON in High gain**

| LNA                                 | VCC7  | All Bands         | 8.6 mA  |

|-------------------------------------|-------|-------------------|---------|

| IQ demodulator                      | VCC8  | All Bands         | 8.4 mA  |

|                                     |       | GSM850 / GSM900   | 18.4 mA |

| LO generation                       | VCC5  | DCS1800 / PCS1900 | 20.2 mA |

| Baseband strip                      | VCC12 | All Bands         | 8.0 mA  |

| Main Prescaler + Main CP + Main PFD | VCC2  | All Bands         | 5.3 mA  |

| Main loop filter                    | VCC3  | All Bands         | 1.7 mA  |

| Voltage regulator R1                | VREG1 | All Bands         | 15.9 mA |

| Voltage regulator R2                | VREG2 | GSM850 / GSM900   | 25.4 mA |

|                                     |       | DCS1800 / PCS1900 | 27.2 mA |

| Voltage regulator R3                | VREG3 | All Bands         | 8.4 mA  |

| VBAT1                               | -     | GSM850 / GSM900   | 43.5 mA |

|                                     |       | DCS1800 / PCS1900 | 45.4 mA |

| VBAT2                               | -     | All Bands         | 8.9 mA  |

TI – Proprietary Information –

Page 17 of 71

| Module | VCC line | Band | Typical operating |

|--------|----------|------|-------------------|

|        |          |      | current           |

#### **TX ON**

| TX Charge pump                                                          | VCC13 | All Bands | 0.8 mA  |

|-------------------------------------------------------------------------|-------|-----------|---------|

| Offset mixer and following low pass filter                              | VCC7  | All Bands | 11.7 mA |

| IQ modulator + post IQ<br>modulator low pass filter                     | VCC12 | All Bands | 8.8 mA  |

| TX VCO + Offset mixer                                                   | VCC10 | Low Band  | 18.2 mA |

| buffer                                                                  |       | High Band | 18.1 mA |

| TX VCO buffer                                                           | VCC8  | Low Band  | 24.4 mA |

|                                                                         |       | High Band | 15.7 mA |

| PA controller                                                           | VCC7  | All Bands | 2.8 mA  |

| LO generation (L divider, M                                             | VCC5  | Low Band  | 26.6 mA |

| divider) + Main VCO<br>regulator input                                  |       | High Band | 26.8 mA |

| Main Prescaler + Main<br>charge pump + Main phase<br>frequency detector | VCC2  | All Bands | 5.3 mA  |

| Main loop filter                                                        | VCC3  | All Bands | 1.7 mA  |

| Voltage regulator R1                                                    | VREG1 | All Bands | 24.1 mA |

| Voltage regulator R2                                                    | VREG2 | Low Band  | 33.6 mA |

|                                                                         |       | High Band | 33.8 mA |

| Voltage regulator R3                                                    | VREG3 | Low Band  | 42.6 mA |

|                                                                         |       | High Band | 33.8 mA |

| VBAT1                                                                   | -     | Low Band  | 70.6 mA |

|                                                                         |       | High Band | 70.4 mA |

| VBAT2                                                                   | -     | Low Band  | 44.9 mA |

|                                                                         |       | High Band | 35.6 mA |

TI – Proprietary Information –

Page 18 of 71

#### **VOLTAGE REGULATION**

C<sub>out</sub>=1.0uF, C<sub>bandgap</sub>=100nF unless otherwise specified.

Table specifies regulator and bandgap together unless otherwise specified.

If an external regulation is desired, the internal voltage regulators can be bypassed (regulators shut down).

| Parameters                                    | Test conditions                                                                                          | Symbol  | Min.      | Тур.             | Max.       | Unit  |  |  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|---------|-----------|------------------|------------|-------|--|--|

| Band gap                                      |                                                                                                          |         |           |                  |            |       |  |  |

| Turn-on time                                  | speed up mode active                                                                                     |         |           |                  | 25         | ms    |  |  |

| Consumption current                           |                                                                                                          |         |           | 80               |            | uA    |  |  |

| Regulator R1                                  | Regulator R1                                                                                             |         |           |                  |            |       |  |  |

| Input voltage                                 |                                                                                                          | Vin     | $3.0^{5}$ | 3.6              | 5.5        | V     |  |  |

| Output voltage                                | @ Ioutmax                                                                                                | Vout    | 2.7       | 2.8              | 2.9        | V     |  |  |

| Max. output current                           |                                                                                                          | Ioutmax | 60        |                  |            | mA    |  |  |

| Ground pin current                            | @ Ioutmax<br>@ Iout = 0 mA                                                                               |         |           |                  | 6.0<br>0.3 | mA    |  |  |

| DC line regulation                            | From Vinmin to Vinmax @ Ioutmax                                                                          |         |           |                  | 50         | mV    |  |  |

| AC line regulation<br>Overshoot<br>Undershoot | Vin step from Vout + 0.1<br>to Vout + 0.5 in 30 us<br>Vin step from Vout + 0.5<br>to Vout + 0.1 in 30 us |         |           |                  | 20<br>20   | mV    |  |  |

| DC load regulation                            | Iout = 0 mA to Ioutmax                                                                                   |         |           |                  | 50         | mV    |  |  |

| AC load regulation<br>Overshoot<br>Undershoot | Iout step from Ioutmax to<br>Ioutmax/2 in 5 us<br>Iout step from Ioutmax/2 to<br>Ioutmax in 5 us         |         |           |                  | 30<br>30   | mV    |  |  |

| Output voltage noise                          | f =10 Hz to 100 kHz<br>Iout = Ioutmax<br>Vin = Vout + 0.2 V                                              |         |           | 50               |            | uVrms |  |  |

| ESR of decoupling capacitor                   |                                                                                                          |         | 0.01      |                  | 1          | Ohm   |  |  |

| Response time                                 | Iout step from 0 to Ioutmax<br>Iout step from Ioutmax to 0<br>@ Vout = final +/-3 %                      |         |           | 10<br>10         |            | us    |  |  |

| Turn-on time                                  | Vout step from 0 to<br>Voutmax +/-3%<br>@ Ioutmax                                                        |         |           | 100 <sup>6</sup> |            | us    |  |  |

| Ripple rejection                              | AC amplitude = 50 mVp<br>f = 100 Hz @ Ioutmax<br>f = 500 kHz @ Ioutmax<br>Vin = 3.1 V                    |         |           | 55<br>35         |            | dB    |  |  |

| Shutdown supply current                       | Vout = 0 V                                                                                               |         |           |                  | 1          | uA    |  |  |

<sup>&</sup>lt;sup>5</sup> 3.0 V corresponds to VBATMIN ==> When MS is emitting at full power, the battery voltage must never be under 3.0 V at Rita regulators inputs

<sup>&</sup>lt;sup>6</sup> Band gap turn-on time not included

TI - Proprietary Information -

Page 19 of 71

| Parameters                                    | Test conditions                                                                                          | Symbol  | Min.      | Тур.             | Max.       | Unit  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|---------|-----------|------------------|------------|-------|

| Regulator R2                                  |                                                                                                          |         |           |                  |            |       |

| Input voltage                                 |                                                                                                          | Vin     | $3.0^{7}$ | 3.6              | 5.5        | V     |

| Output voltage                                | @ Ioutmax                                                                                                | Vout    | 2.7       | 2.8              | 2.9        | V     |

| Max. output current                           |                                                                                                          | Ioutmax | 60        |                  |            | mA    |

| Ground pin current                            | @ Ioutmax<br>@ Iout = 0 mA                                                                               |         |           |                  | 6.0<br>0.3 | mA    |

| DC line regulation                            | From Vinmin to Vinmax @ Ioutmax                                                                          |         |           |                  | 50         | mV    |

| AC line regulation<br>Overshoot<br>Undershoot | Vin step from Vout + 0.1<br>to Vout + 0.5 in 30 us<br>Vin step from Vout + 0.5<br>to Vout + 0.1 in 30 us |         |           |                  | 20<br>20   | mV    |

| DC load regulation                            | Iout = 0  mA to Ioutmax                                                                                  |         |           |                  | 50         | mV    |

| AC load regulation<br>Overshoot<br>Undershoot | Iout step from Ioutmax to<br>Ioutmax/2 in 5 us<br>Iout step from Ioutmax/2 to<br>Ioutmax in 5 us         |         |           |                  | 30<br>30   | mV    |

| Output voltage noise                          | f =10 Hz to 100 kHz<br>Iout = Ioutmax<br>Vin = Vout + 0.2 V                                              |         |           | 50               |            | uVrms |

| ESR of decoupling capacitor                   |                                                                                                          |         | 0.01      |                  | 1          | Ohm   |

| Response time                                 | Iout step from 0 to Ioutmax<br>Iout step from Ioutmax to 0<br>@ Vout = final +/-3 %                      |         |           | 10<br>10         |            | us    |

| Turn-on time                                  | Vout step from 0 to<br>Voutmax +/-3%<br>@ Ioutmax                                                        |         |           | 100 <sup>8</sup> |            | us    |

| Ripple rejection                              | AC amplitude = 50 mVp<br>f = 100 Hz @ Ioutmax<br>f = 500 kHz @ Ioutmax<br>Vin = 3.1 V                    |         |           | 55<br>35         |            | dB    |

| Shutdown supply current                       | Vout = 0 V                                                                                               |         |           |                  | 1          | uA    |

<sup>&</sup>lt;sup>8</sup> Band gap turn-on time not included

TI - Proprietary Information -

Page 20 of 71

$<sup>^7</sup>$  3.0 V corresponds to VBATMIN ==> When MS is emitting at full power, the battery voltage must never be under 3.0 V at Rita regulators inputs

| Parame ters                                   | Test conditions                                                                                          | Symbol  | Min.      | Тур.              | Max.       | Unit  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------|---------|-----------|-------------------|------------|-------|

| Regulator R3                                  |                                                                                                          |         |           |                   |            |       |

| Input voltage                                 |                                                                                                          | Vin     | $3.0^{9}$ | 3.6               | 5.5        | V     |

| Output voltage                                | @ Ioutmax                                                                                                | Vout    | 2.7       | 2.8               | 2.9        | V     |

| Max. output current                           |                                                                                                          | Ioutmax | 60        |                   |            | mA    |

| Ground pin current                            | @ Ioutmax<br>@ Iout = 0 mA                                                                               |         |           |                   | 6.0<br>0.3 | mA    |

| DC line regulation                            | From Vinmin to Vinmax @ Ioutmax                                                                          |         |           |                   | 50         | mV    |

| AC line regulation<br>Overshoot<br>Undershoot | Vin step from Vout + 0.1<br>to Vout + 0.5 in 30 us<br>Vin step from Vout + 0.5<br>to Vout + 0.1 in 30 us |         |           |                   | 20<br>20   | mV    |

| DC load regulation                            | Iout = 0 mA to Ioutmax                                                                                   |         |           |                   | 50         | mV    |

| AC load regulation<br>Overshoot<br>Undershoot | Iout step from Ioutmax to<br>Ioutmax/2 in 5 us<br>Iout step from Ioutmax/2 to<br>Ioutmax in 5 us         |         |           |                   | 30<br>30   | mV    |

| Output voltage noise                          | f =10 Hz to 100 kHz<br>Iout = Ioutmax<br>Vin = Vout + 0.2 V                                              |         |           | 50                |            | uVrms |

| ESR of decoupling capacitor                   |                                                                                                          |         | 0.01      |                   | 1          | Ohm   |

| Response time                                 | Iout step from 0 to Ioutmax<br>Iout step from Ioutmax to 0<br>@ Vout = final +/-3 %                      |         |           | 10<br>10          |            | us    |

| Turn-on time                                  | Vout step from 0 to<br>Voutmax +/-3%<br>@ Ioutmax                                                        |         |           | 100 <sup>10</sup> |            | us    |

| Ripple rejection                              | AC amplitude = 50 mVp<br>f = 100 Hz @ Ioutmax<br>f = 500 kHz @ Ioutmax<br>Vin = 3.1 V                    |         |           | 55<br>35          |            | dB    |

| Shutdown supply current                       | Vout = 0 V                                                                                               |         |           |                   | 1          | uA    |

<sup>&</sup>lt;sup>10</sup> Band gap turn-on time not included

TI - Proprietary Information -

Page 21 of 71

$<sup>^9</sup>$  3.0 V corresponds to VBATMIN ==> When MS is emitting at full power, the battery voltage must never be under 3.0 V at Rita regulators inputs

#### **Regulators power domains**

| Functional blocks                                                                                           | Supply voltage                           | Regulated Supply        | VCC line            |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------|---------------------|

| Receiver                                                                                                    |                                          |                         |                     |

| LNAGSM, LNADCS, LNAPCS                                                                                      | VBAT1                                    | Vreg1                   | VCC7                |

| Analog part of VGA                                                                                          | VBAT1                                    | Vreg1                   | VCC12               |

| IQ demodulators (MIXGSM, MIXDCS and MIXPCS)                                                                 | VBAT2                                    | Vreg3                   | VCC8                |

| Interferer detection system                                                                                 | VBAT2                                    | Vreg3                   | VCC10               |

| Transmitter                                                                                                 |                                          |                         |                     |

| Charge pump                                                                                                 | VBAT1                                    | Vreg1                   | VCC13               |

| Phase frequency detector                                                                                    | VBAT1                                    | Vreg1                   | _11                 |

| Offset mixer, post offset mixer low pass filter                                                             | VBAT1                                    | Vreg1                   | VCC7                |

| Offset mixer buffer                                                                                         | VBAT2                                    | Vreg3                   | VCC10               |

| IQ modulator, post IQ modulator low pass filter                                                             | VBAT1                                    | Vreg1                   | VCC12               |

| TX LB VCO                                                                                                   | VCC10                                    | 2.4V internal regulator | VCC11 <sup>12</sup> |

| TX HB VCO                                                                                                   | VCC10                                    | 2.4V internal regulator | VCC9 <sup>12</sup>  |

| TX VCO output buffers                                                                                       | VBAT2                                    | Vreg3                   | VCC8                |

| PA controller                                                                                               | VBAT1                                    | Vreg1                   | VCC7                |

| Main synthesizer                                                                                            |                                          |                         |                     |

| Prescaler, Charge pump, Phase frequency detector                                                            | VBAT1                                    | Vreg2                   | VCC2                |

| Loop filter (operational amplifier)                                                                         | VBAT1                                    | Vreg2                   | VCC3                |

| Counters A, B                                                                                               | VBAT1                                    | Vreg2                   | VCC1                |

| LO generation for the RX/TX (L divider, M divider)                                                          | VBAT1                                    | Vreg2                   | VCC5                |

| MAIN VCO2                                                                                                   | VCC5                                     | 2.0V internal regulator | VCC4 <sup>13</sup>  |

| MAIN VCO1                                                                                                   | VCC5                                     | 2.0V internal regulator | VCC6 <sup>13</sup>  |

| VCO calibration machine                                                                                     | VBAT2                                    | Vreg3                   | VCC10               |

| Reference voltage source                                                                                    |                                          |                         |                     |

| Band gap                                                                                                    | VBAT2                                    | -                       | -                   |

| Digital control                                                                                             |                                          | •                       |                     |

| PA controller timer, Digital clock generator, serial interface and associated buffer, VGA digital circuitry | VRIO supply from ABB chip                | -                       | VRIO                |

| Internal 26MHz VCXO                                                                                         |                                          |                         |                     |

| VCXO core, Main PLL Reference divider                                                                       | TCXOEN buffer<br>(2.7V) from DBB<br>chip | -                       | XEN                 |

| Internal VCXO selection                                                                                     | TCXOEN buffer<br>(2.7V) from DBB<br>chip | -                       | XSEL                |

| RF front End module (external component)                                                                    |                                          |                         |                     |

| Front End Module                                                                                            | VBAT2                                    | Vreg3                   | -                   |

<sup>13</sup> Decoupling line for 2.0V internal regulator output

TI - Proprietary Information -

Page 22 of 71

<sup>11</sup> Connection is done on chip (no decoupling using a VCC line)

<sup>&</sup>lt;sup>12</sup> Decoupling line for 2.4V internal regulator output

| Parameters Test conditions Symbol Min. Typ. M | Max. Unit |

|-----------------------------------------------|-----------|

|-----------------------------------------------|-----------|

# TEMPERAT URE SENSOR<sup>14</sup>

| Sensor voltage | @ Ta min. = $-25^{\circ}$ C | 0.9  | 1.05 | V    |

|----------------|-----------------------------|------|------|------|

|                | @ Ta max. = $+85^{\circ}$ C | 1.35 | 1.5  |      |

| Sensor slope   | Over $-25 \sim +85$ °C      | 3.5  | 4.5  | V/°C |

#### **SYNTHESIZER**

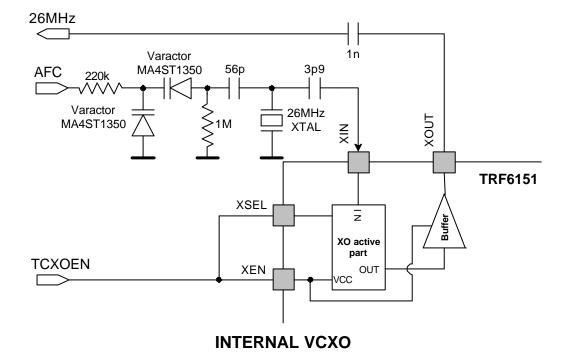

#### Crystal and External Varactor network 15

| XEN supply pin                             | @ I = 2.0mA                                                      |    | 2.5   |       | 2.9          | V          |

|--------------------------------------------|------------------------------------------------------------------|----|-------|-------|--------------|------------|

| Crystal                                    |                                                                  |    |       |       |              |            |

| Nominal frequency                          |                                                                  |    |       | 26.0  |              | MHz        |

| Frequency tolerance                        | at 25°C±3°C                                                      |    |       |       | ±10.0        | ppm        |

| Temperature characteristics                | in reference to $+25^{\circ}$ C<br>over $-20 \sim +75^{\circ}$ C |    |       |       | ±10.0        | ppm        |

| Aging 1 <sup>st</sup> year after 5 years   |                                                                  |    |       |       | ±1.0<br>±2.5 | ppm<br>ppm |

| Dips vs. temperature                       | $-20 \sim +75^{\circ} \text{C}$                                  |    |       |       | 0.3          | ppm/°C     |

| Frequency versus temperature slope at 25°C | at 25° C ± 7°C                                                   |    | -0.5  |       | 0            | ppm/°C     |

| Equivalent Series<br>Resistance            |                                                                  |    | 0     |       | 40           | Ω          |

| Standard load capacitance                  |                                                                  |    |       | 9.3   | 12.0         | pF         |

| Shunt capacitance                          |                                                                  |    |       | 1.5   | 1.7          | pF         |

| Motional capacitance                       |                                                                  |    | 5.4   | 6.3   | 7.2          | fF         |

| Drive level                                |                                                                  |    |       |       | 150          | μW         |

| Varactor network                           |                                                                  |    |       |       |              |            |

| Voltage tuning                             |                                                                  | Vt | 0     |       | 2.0          | V          |

| Tuning range                               |                                                                  |    | ±26.0 | ±33.0 | ±41.0        | ppm        |

| Sensitivity accuracy <sup>16</sup>         | Over temp and over the tuning range                              |    |       |       | 20 %         | Hz/step^2  |

| Frequency step                             |                                                                  |    |       |       | 0.01         | ppm/step   |

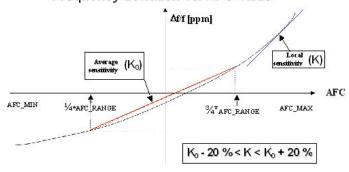

#### Frequency deviation vs. AFC value

<sup>&</sup>lt;sup>14</sup> This temperature sensor is accessible at any time (not multiplexed with another signal)

<sup>&</sup>lt;sup>16</sup> The sensitivity accuracy is how much the "local sensitivity" can differ from the average sensitivity. In other words, it is the derivate of the sensitivity. See the plot above.

TI - Proprietary Information -

Page 23 of 71

<sup>&</sup>lt;sup>15</sup> See Annex 6 (page 67) for connection schematic

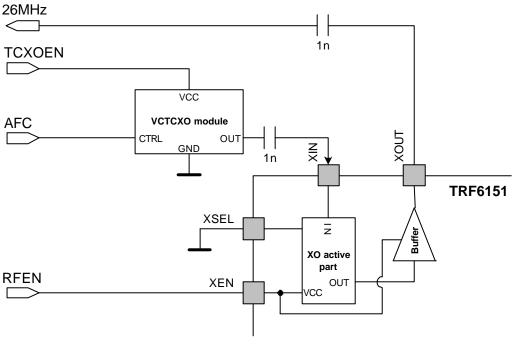

## Reference clock input<sup>17</sup>

| Input frequency       |                |     | 26  |       | MHz    |

|-----------------------|----------------|-----|-----|-------|--------|

| Input sensitivity     |                | 0.5 | 1.0 | 2.0   | Vpp    |

| Reference phase noise | @ 1 kHz offset |     |     | -129  | dBc/Hz |

| Duty cycle            |                |     |     | 40/60 |        |

|                       |                |     |     | to    |        |

|                       |                |     |     | 60/40 |        |

| Input resistance      |                | 10  |     |       | kΩ     |

| Input capacitance     |                |     |     | 5     | pF     |

## VCXO buffer output (XOUT pin)<sup>18</sup>

| Output frequency |  |     | 26  |     | MHz |

|------------------|--|-----|-----|-----|-----|

| Output level     |  | 0.5 | 1.0 | 2.0 | Vpp |

$<sup>^{18}</sup>$   $Z_{LOAD}$  = 25pF in parallel with  $10k\Omega$  @ 26MHz

TI - Proprietary Information -

Page 24 of 71

**Strictly Private**

$<sup>^{17}</sup>$  If use of an external VCTCXO (See Annex 6 (page 67) for connection schematic)

| Parameters | Test conditions | Symbol | Min. | Тур. | Max. | Unit | l |

|------------|-----------------|--------|------|------|------|------|---|

|------------|-----------------|--------|------|------|------|------|---|

#### Main synthesizer in RX mode for GSM 850 and E-GSM 900

Specification at the mixers LO port

| Specification at the mix  | kers LO port                |      |     |      |        |

|---------------------------|-----------------------------|------|-----|------|--------|

| Prescaler input frequency |                             | 3476 |     |      | MHz    |

| range                     |                             | to   |     |      |        |

|                           |                             | 3840 |     |      |        |

| PFD operating frequency   |                             |      | 400 |      | kHz    |

| N divider ratio           |                             | 8692 |     |      |        |

|                           |                             | to   |     |      |        |

|                           |                             | 9598 |     |      |        |

| L divider by 4 output     |                             | 869  |     |      | MHz    |

| frequency range           |                             | to   |     |      |        |

|                           |                             | 960  |     |      |        |

| Close in phase noise      | @ 1 kHz offset              |      |     | -81  | dBc/Hz |

|                           | fcomp = 400  kHz            |      |     |      |        |

|                           | @ 960 MHz                   |      |     |      |        |

| Phase noise               | @ 600 kHz offset            |      |     | -120 | dBc/Hz |

|                           | @ 1.6 MHz offset            |      |     | -135 |        |

|                           | @ 3.0 MHz offset            |      |     | -140 |        |

|                           | @ 10 MHz offset             |      |     | -142 |        |

|                           | @ 20 MHz offset             |      |     | -145 |        |

| Reference feedthrough     | @ 400 kHz offset            |      |     | -53  | dBc    |

|                           | @ 800 kHz offset            |      |     | -68  |        |

|                           | @ 1.6 MHz offset            |      |     | -79  |        |

| Lock time                 | 1) GSM850:                  |      | tbd | 170  | us     |

|                           | From 869MHz to 894MHz       |      |     |      |        |

|                           | 2) GSM900:                  |      |     |      |        |

|                           | From 925MHz to 960MHz       |      |     |      |        |

|                           | 3) PCS1900 <b>→</b> GSM850: |      |     |      |        |

|                           | From 1990MHz to 869MHz      |      |     |      |        |

|                           | 4) DCS1800 → GSM900:        |      |     |      |        |

|                           | From 1880MHz to 925MHz      |      |     |      |        |

|                           | @ 20 Hz averaged            |      |     |      |        |

|                           | frequency error over one    |      |     |      |        |

|                           | burst                       |      |     |      |        |

Power up/down time

| Power up time   | Output power within 10 % |  |  | 5 | us |

|-----------------|--------------------------|--|--|---|----|

|                 | of steady state values   |  |  |   |    |

| Power down time |                          |  |  | 5 | us |

TI - Proprietary Information -

Page 25 of 71

#### Main synthesizer in RX mode for DCS 1800 and PCS 1900

Specification at the mixers LO port

| Specification at the mix  | ers LO port                | T | 1    | r   |      | r      |

|---------------------------|----------------------------|---|------|-----|------|--------|

| Prescaler input frequency |                            |   | 3610 |     |      | MHz    |

| range                     |                            |   | to   |     |      |        |

|                           |                            |   | 3980 |     |      |        |

| PFD operating frequency   |                            |   |      | 400 |      | kHz    |

| N divider ratio           |                            |   | 9026 |     |      |        |

|                           |                            |   | to   |     |      |        |

|                           |                            |   | 9949 |     |      |        |

| L divider by 2 output     |                            |   | 1805 |     |      | MHz    |

| frequency range           |                            |   | to   |     |      |        |

|                           |                            |   | 1990 |     |      |        |

| Close in phase noise      | @ 1 kHz offset             |   |      |     | -81  | dBc/Hz |

|                           | fcomp = 400 kHz            |   |      |     |      |        |

|                           | @ 1990 MHz                 |   |      |     |      |        |

| Phase noise               | @ 600 kHz offset           |   |      |     | -120 | dBc/Hz |

|                           | @ 1.6 MHz offset           |   |      |     | -132 |        |

|                           | @ 3.0 MHz offset           |   |      |     | -137 |        |

|                           | @ 20 MHz offset            |   |      |     | -146 |        |

| Reference feedthrough     | @ 400 kHz offset           |   |      |     | -53  | dBc    |

|                           | @ 800 kHz offset           |   |      |     | -69  |        |

|                           | @ 1.6 MHz offset           |   |      |     | -82  |        |

| Lock time                 | 1) DCS1800:                |   |      | tbd | 170  | us     |

|                           | From 1805MHz to 1880MHz    |   |      |     |      |        |

|                           | 2) PCS1900:                |   |      |     |      |        |

|                           | From 1930MHz to 1990MHz    |   |      |     |      |        |

|                           | 3) GSM850 → PCS1900:       |   |      |     |      |        |

|                           | From 869MHz to 1990MHz     |   |      |     |      |        |

|                           | 4) GSM900 → DCS1800:       |   |      |     |      |        |

|                           | From 925MHz to 1880MHz     |   |      |     |      |        |

|                           | @ 40 Hz averaged frequency |   |      |     |      |        |

|                           | error over one burst       |   |      |     |      |        |

Power up/down time

| Power up time   | Output power within 10 % of |  |  | 5 | us |

|-----------------|-----------------------------|--|--|---|----|

|                 | steady state values         |  |  |   |    |

| Power down time |                             |  |  | 5 | us |

TI - Proprietary Information -

Page 26 of 71

| Parameters Test conditions Symbol Min. Typ. Max. | Min.   Typ.   Max.   Unit |  | Test conditions | Parameters |

|--------------------------------------------------|---------------------------|--|-----------------|------------|

|--------------------------------------------------|---------------------------|--|-----------------|------------|

#### Main synthesizer in TX mode for GSM 850 and E-GSM 900

Specification at the offset mixer LO port

| Prescaler input frequency range       |                                                                                          | 69 to<br>957 |                            |                   | MHz    |

|---------------------------------------|------------------------------------------------------------------------------------------|--------------|----------------------------|-------------------|--------|

| PFD operating frequency               | For GSM 850:<br>[824.2 ~ 837.0 MHz]<br>[837.2 ~ 848.8 MHz]<br>For GSM 900                |              | 472.73<br>866.67<br>742.86 |                   | kHz    |

| N divider ratio                       |                                                                                          | 36 to<br>370 |                            |                   |        |

| L divider by 4 output frequency range |                                                                                          | 7 to<br>90   |                            |                   | MHz    |

| M divider ratio                       | For GSM 850:<br>[824.2 ~ 837.0 MHz]<br>[837.2 ~ 848.8 MHz]<br>For GSM 900                |              | 26<br>52<br>52             |                   |        |

| M divider output frequency range      |                                                                                          | 2 to<br>53   |                            |                   | MHz    |

| Close in phase noise                  | GSM850:<br>@ 1 kHz offset<br>fcomp = 472.73 kHz<br>@ 990 MHz                             |              |                            | -81               | dBc/Hz |

|                                       | GSM900:<br>@ 1 kHz offset<br>fcomp = 742.86 kHz<br>@ 850 MHz                             |              |                            | -81               |        |

| Phase noise                           | @ 400 kHz offset                                                                         |              |                            | -120              | dBc/Hz |

| Reference feedthrough                 | GSM 850:<br>@ 472.73 kHz offset<br>@ 866.67 kHz offset<br>GSM900:<br>@ 742.86 kHz offset |              |                            | -69<br>-67<br>-67 | dBc    |

| Lock time                             | @ 20 Hz averaged frequency error over one burst                                          |              | tbd                        | 235               | us     |

#### Power up/down time

| Power up time   | Output power within 10 % of steady state values |  | 5 | us |

|-----------------|-------------------------------------------------|--|---|----|

| Power down time | j                                               |  | 5 | us |

TI - Proprietary Information -

Page 27 of 71

| Parameters Test conditions | Symbol Min. | Typ. Max. | Unit |

|----------------------------|-------------|-----------|------|

|----------------------------|-------------|-----------|------|

#### Main synthesizer in TX mode for DSC 1800 and PCS 1900

Specification at the offset mixer LO port

| Specification at the offset | t mixer 20 port          | 1 10151 | Ī      |      |        |

|-----------------------------|--------------------------|---------|--------|------|--------|

| Prescaler input frequency   |                          | 3176 to |        |      | MHz    |

| range                       |                          | 3547    |        |      |        |

| PFD operating frequency     |                          |         | 371.43 |      | kHz    |

| N divider ratio             |                          | 8551    |        |      |        |

|                             |                          | to 9549 |        |      |        |

| L divider by 2 output       |                          | 1588 to |        |      | MHz    |

| frequency range             |                          | 1774    |        |      |        |

| M divider ratio             |                          |         | 26     |      |        |

| M divider output frequency  |                          | 122 to  |        |      | MHz    |

| range                       |                          | 137     |        |      |        |

| Close in phase noise        | @ 1 kHz offset           |         |        | -81  | dBc/Hz |

| _                           | fcomp = 371.43 kHz       |         |        |      |        |

|                             | @ 1774 MHz               |         |        |      |        |

| Phase noise                 | @ 400 kHz offset         |         |        | -120 | dBc/Hz |

| Reference feedthrough       | @ 371.43 kHz offset      |         |        | -69  | dBc    |

| Lock time                   | @ 40 Hz averaged         |         | tbd    | 235  | us     |

|                             | frequency error over one |         |        |      |        |

|                             | burst                    |         |        |      |        |

#### Synthesizer Power up / down time

| Power up time   | Output power within 10 % of steady state values |  | 5 | us |

|-----------------|-------------------------------------------------|--|---|----|

| Power down time |                                                 |  | 5 | us |

TI - Proprietary Information -

Page 28 of 71

| Parameters | Test conditions | Symbol | Min. | Тур. | Max. | Unit |

|------------|-----------------|--------|------|------|------|------|

|            |                 |        |      |      |      | 1    |

#### **TRANSMITTER**

#### **Transmitter inputs**

| I/Q inputs common mode voltage |                    | 1.215 | 1.35 | 1.485 | V   |

|--------------------------------|--------------------|-------|------|-------|-----|

| I/Q inputs voltage<br>swing    | Single ended       | 0.44  | 0.47 | 0.49  | Vpp |

| I/Q inputs resistance          | Differential ended | 10    |      |       | kO  |

| I/Q inputs capacitance         | Differential ended |       |      | 25    | pF  |

#### **Low Band Output**

Dedicated to GSM850 and E-GSM900

GMSK modulated signal applied at the IQ inputs (unless otherwise specified)

| Frequency range    |                       | f <sub>out</sub> | 824.2 to |     |     | MHz    |

|--------------------|-----------------------|------------------|----------|-----|-----|--------|

| 1 . 0              |                       |                  | 914.8    |     |     |        |

| Output impedance   |                       | Z <sub>out</sub> |          | 50  |     | О      |

| Output Return Loss |                       |                  |          |     | -10 | dB     |

| Output power level | into 50 O load        | P <sub>out</sub> | 4        | 6   | 8   | dBm    |

| Phase error        | Max. RMS phase error  |                  |          |     | 3   | degree |

|                    | Max. Peak phase error |                  |          |     | 10  |        |

| TXVCOLB Pulling    | VSWR = 2, all phases, | PULL             |          | tbd |     | MHz    |

|                    | open loop             |                  |          |     |     |        |

TI - Proprietary Information -

Page 29 of 71

| Parameters     | Test conditions  | Symbol   | Min.   | Tvp.   | Max.     | Unit  |

|----------------|------------------|----------|--------|--------|----------|-------|

| I di dilictors | 1 cot containing | 53111501 | 1,1111 | - J P. | 11164280 | CILIC |

#### **Low Band Output (continued)**

68 kHz CW signal applied at the IQ inputs (unless otherwise specified)

|                             | approva at the 16 mbate (                     |                   |     | ,    |                    |        |

|-----------------------------|-----------------------------------------------|-------------------|-----|------|--------------------|--------|

| Carrier Suppression         | With respect to the carrier                   | CS                | -35 |      |                    | dBc    |

| Sideband                    | With respect to the carrier                   | SBS               | -40 |      |                    | dBc    |

| Suppression                 |                                               |                   |     |      |                    |        |

| Spurs @ 4×fIQ               | With respect to the carrier                   | S4C               | -50 |      |                    | dBc    |

| Phase Noise                 | @ 400 kHz offset from                         | $PN_{400}$        |     | -117 | -113               | dBc/Hz |

|                             | the carrier @ 20 MHz offset from the carrier  | PN <sub>20M</sub> |     |      | -164 <sup>19</sup> |        |

| Settling time <sup>20</sup> | From power down to final                      |                   |     |      | 240                | us     |

|                             | frequency @ 20 Hz<br>averaged frequency error |                   |     |      |                    |        |

|                             | over one burst                                |                   |     |      |                    |        |

<sup>&</sup>lt;sup>20</sup> Including settling time of the MAIN PLL

TI - Proprietary Information -

Page 30 of 71

$<sup>^{19}</sup>$  Measured with a Spectrum Analyzer as defined by ETSI norm – No corrective factor applied – The specification of –164dBc/Hz with +6dBm output power is equivalent to a measurement of –108dBm into 100kHz RBW

| Parameters Test conditions | Symbol | Min. | Тур. | Max. | Unit |  |

|----------------------------|--------|------|------|------|------|--|

|----------------------------|--------|------|------|------|------|--|

#### **High Band Output**

Dedicated to DCS1800 and PCS 1900

GMSKmodulated signal applied at the IQ inputs (unless otherwise specified)

| Frequency range    |                       | $f_{out}$        | 1710.2 |     |     | MHz    |

|--------------------|-----------------------|------------------|--------|-----|-----|--------|

|                    |                       |                  | to     |     |     |        |

|                    |                       |                  | 1909.8 |     |     |        |

| Output impedance   |                       | Z <sub>out</sub> |        | 50  |     | О      |

| Output Return Loss |                       |                  |        |     | -10 | dB     |

| Output power level | into 50 O load        | P <sub>out</sub> | 4      | 6   | 8   | dBm    |

| Phase error        | Max. RMS phase error  |                  |        |     | 3   | degree |

|                    | Max. Peak phase error |                  |        |     | 10  |        |

| TXVCOHB Pulling    | VSWR = 2, all phases, | PULL             |        | tbd |     | MHz    |

|                    | open loop             |                  |        |     |     |        |

TI - Proprietary Information -

Page 31 of 71

**Strictly Private**

| Parameters | Test conditions | Symbol | Min. | Тур. | Max. | Unit | ĺ |

|------------|-----------------|--------|------|------|------|------|---|

|------------|-----------------|--------|------|------|------|------|---|

#### **High Band Output (continued)**

68 kHz CW signal applied at the IQ inputs (unless otherwise specified)

|                             | applied at the 1Q inputs | (          |     |      |                    |        |

|-----------------------------|--------------------------|------------|-----|------|--------------------|--------|

| Carrier Suppression         | With respect to the      | CS         | -35 |      |                    | dBc    |

|                             | carrier                  |            |     |      |                    |        |

| Sideband                    | With respect to the      | SBS        | -40 |      |                    | dBc    |

| Suppression                 | carrier                  |            |     |      |                    |        |

| Spurs @ 4×fIQ               | With respect to the      | S4C        | -50 |      |                    | dBc    |

|                             | carrier                  |            |     |      |                    |        |

| Phase Noise                 | @ 400 kHz offset from    | $PN_{400}$ |     | -117 | -113               | dBc/Hz |

|                             | the carrier              |            |     |      |                    |        |

|                             | @ 20 MHz offset from     | $PN_{20M}$ |     |      | -152 <sup>21</sup> |        |

|                             | the carrier              |            |     |      |                    |        |

| Settling time <sup>22</sup> | From power down to       |            |     |      | 240                | us     |

|                             | final frequency @ 40 Hz  |            |     |      |                    |        |

|                             | averaged frequency       |            |     |      |                    |        |

|                             | error over one burst     |            |     |      |                    |        |

<sup>&</sup>lt;sup>22</sup> Including settling time of the MAIN PLL

TI - Proprietary Information -

Page 32 of 71

$<sup>^{21}</sup>$  Measured with a SpectrumAnalyzer as defined by ETSI norm – No corrective factor applied – The specification of -152dBc/Hz with +6dBm output power is equivalent to a measurement of -96dBm into 100kHz RBW

$>= 6.0 \text{ MHz offset}^{24}$

| Parameters        | Test conditions                              | Symbol | Min. | Тур. | Max. | Unit |

|-------------------|----------------------------------------------|--------|------|------|------|------|

|                   |                                              |        |      |      |      |      |

| Madulated autout  | on o o trum                                  |        |      |      |      |      |

| Modulated output  | spectrum                                     |        |      |      |      |      |

| GSM 850 / E-GSM 9 | 000                                          |        |      |      |      |      |

| Maximum allowed   | @ 200 kHz offset <sup>23</sup>               |        |      |      | -30  | dBc  |

| level             | @ 250 kHz offset <sup>23</sup>               |        |      |      | -33  | dBc  |

|                   | @ 400 kHz offset <sup>23</sup>               |        |      | -64  | -60  | dBc  |

|                   | >= 600 kHz < 1.8 MHz                         |        |      |      | -60  | dBc  |

|                   | offset <sup>23</sup>                         |        |      |      |      |      |

|                   | >= 1.8 MHz < 3.0 MHz offset <sup>24</sup>    |        |      |      | -63  | dBc  |

|                   | >= 3.0 MHz < 6.0 MHz offset <sup>24</sup>    |        |      |      | -65  | dBc  |

|                   | >= 6.0 MHz offset <sup>24</sup>              |        |      |      | -71  | dBc  |

|                   |                                              |        |      |      |      |      |

| DCS 1800          | 72                                           | 1      |      | 1    | 1    | 1    |

| Maximum allowed   | @ 200 kHz offset <sup>23</sup>               |        |      |      | -30  | dBc  |

| level             | @ 250 kHz offset <sup>23</sup>               |        |      |      | -33  | dBc  |