# Calypso/lota/Clara System Application Note

APN0 Ver 1.2

# File: G:\lota\Application Notes\APN0.doc

**Department:** Application Specific Product / Wireless Communications System

|           | Originator                                 | Approval          | Quality |

|-----------|--------------------------------------------|-------------------|---------|

| Name      | Lorenzo Indiani ;J.C.<br>Jiguet;J.C.Perrin | M.Gac<br>P.Perney |         |

| Date      | 09/15/00                                   |                   |         |

| Signature |                                            |                   |         |

TI – Proprietary Information –

PAGE: 1/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

# **HISTORY**

| Version  | Date    | Author    | Notes |

|----------|---------|-----------|-------|

| Ver: 1.0 | 1/20/01 | L.Indiani | 1     |

| Ver: 1.1 | 6/22/01 | L.Indiani | 2     |

| Ver: 1.2 | 7/15/02 | L.Indiani | 3     |

| Ver: 4.0 |         |           | 4     |

# NOTES :

- 1. Creation

- 2. RF and BCI application part rework

- 3. Minor wording change, sleep timing update, LDO voltage update, SIM schematic correction

**TI – Proprietary Information –**

PAGE: 2/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

# **Table of contents**

| 1 | INT        | RODUCTION                                       |    |

|---|------------|-------------------------------------------------|----|

|   | 1.1        | CALYPSO                                         |    |

|   | 1.2        | ЮТА                                             |    |

|   | 1.3        | CLARA                                           | 8  |

| 2 | SYS        | TEM CONNECTIONS                                 |    |

|   | 2.1        | CALYPSO TO CLARA                                |    |

|   | 2.1        | IOTA TO (LARA                                   |    |

|   | 2.2        | CALYPSO TO JOTA                                 |    |

|   | 2.3        |                                                 |    |

|   | 2.3.2      |                                                 |    |

|   | 2.3.3      |                                                 |    |

|   | 2.3.4      |                                                 |    |

|   | 2.3.5      | •                                               |    |

|   | 2.3.6      |                                                 |    |

|   | 2.3.7      | CLOCKS                                          |    |

|   | 2.3.8      | B INTERRUPTS                                    | 15 |

|   | 2.3.9      | POWER MGMNT                                     | 15 |

|   | 2.3.1      | 0 POWER supplies                                | 16 |

|   | 2.3.1      | 1 Calypso Supplies voltages rules               | 18 |

| 3 | POV        | VER SPLIT CONCEPT IN CALYPSO-IOTA SYSTEMS       |    |

|   | 3.1        | SYSTEM POWER ON RESET GENERATION                | 22 |

|   |            |                                                 |    |

| 4 | <b>SYS</b> | TEM MODES                                       |    |

|   | 4.1        | NO SUPPLY                                       |    |

|   | 4.2        | ACTIVE                                          |    |

|   | 4.3        | OFF                                             |    |

|   | 4.4        | BACKUP                                          |    |

|   | 4.5        | SLEEP                                           |    |

| 5 | SYS'       | FEM TRANSITIONS BETWEEN OPERATING MODES         |    |

|   | 5.1        | SUPPLY INSERTION/REMOVAL DRIVEN TRANSITIONS     |    |

|   | 5.1.1      | MB insertion                                    |    |

|   | 5.1.2      | BB insertion                                    |    |

|   | 5.1.3      | MB removal                                      |    |

|   | 5.1.4      |                                                 |    |

|   | 5.2        | HW DRIVEN TRANSITIONS                           |    |

|   | 5.2.1      |                                                 |    |

|   | 5.2.2      | BB low                                          |    |

|   | 5.2.3      | 1 9 8                                           |    |

|   | 5.2.4      |                                                 |    |

|   | 5.2.5      |                                                 |    |

|   | 5.3        | SW DRIVEN TRANSITIONS                           |    |

|   | 5.3.1      |                                                 |    |

|   | 5.3.2      | SLEEP ON                                        |    |

| 6 | CUR        | RENT CONSUMPTION IN BACKUP, OFF AND SLEEP MODES |    |

|   | 6.1        | BACKUP MODE                                     |    |

|   | 6.1.1      |                                                 |    |

|   | 6.1.2      | System with MB                                  |    |

|   |            |                                                 |    |

TI – Proprietary Information –

PAGE: 3/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

|   | 6.2 OF | F MODE                                                         | 45 |

|---|--------|----------------------------------------------------------------|----|

|   | 6.3 SL | EEP MODE                                                       | 45 |

| 7 | APPLIC | CATIONS                                                        | 48 |

|   | 7.1 AN | [ALOG                                                          | 48 |

|   | 7.1.1  | Sim interface                                                  |    |

|   | 7.1.1. | 1 1.8V SIM interface                                           | 48 |

|   | 7.1.1. | 2 SIM card 3V specification                                    | 50 |

|   | 7.1.2  | Optimized Backup scheme                                        |    |

|   | 7.1.3  | Madc                                                           | 55 |

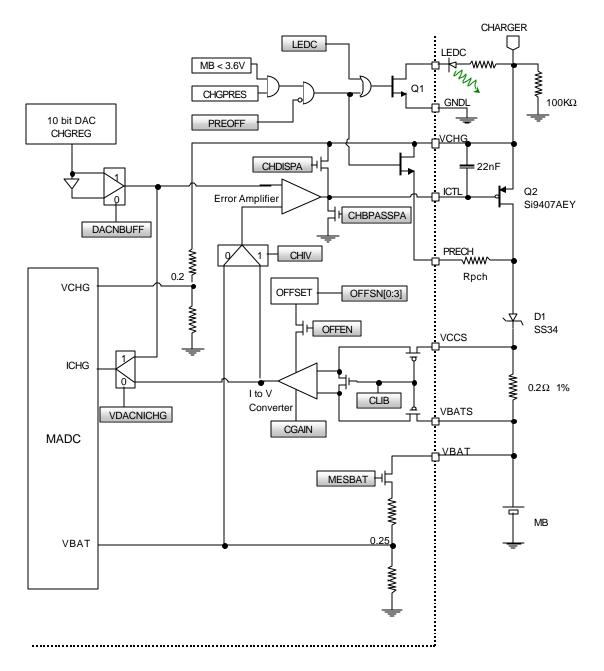

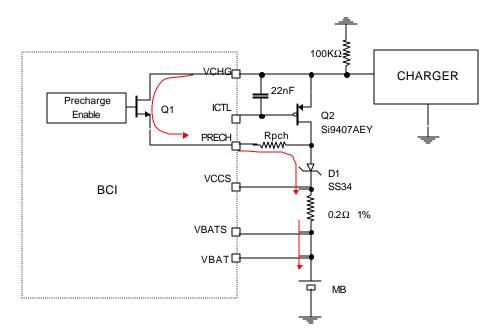

|   | 7.1.4  | Bci                                                            | 56 |

|   | 7.1.4. | 0                                                              |    |

|   | 7.1.4. | 2 Algorithm basis for Li-Ion battery charging.                 | 62 |

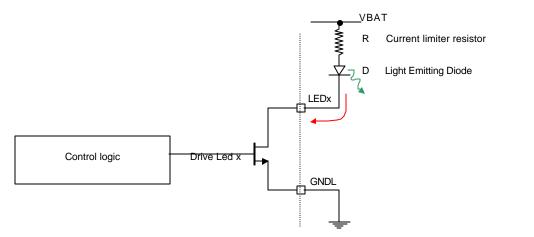

|   | 7.1.5  | Led drivers                                                    | 65 |

|   | 7.1.6  | Audio application schematics                                   |    |

|   | 7.1.6. | · · · · · ·                                                    |    |

|   | 7.1.6. | 1                                                              |    |

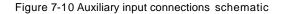

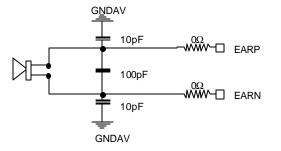

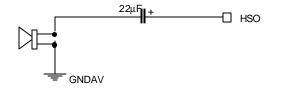

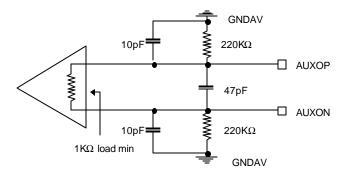

|   | 7.1.6. | 3 Auxiliary Input                                              | 67 |

|   | 7.1.6. | 1                                                              |    |

|   | 7.1.6. | · · · · · · · · · · · · · · · · · · ·                          |    |

|   | 7.1.6. |                                                                |    |

|   |        | GITAL                                                          |    |

|   | 7.2.1  | 32KHz Oscillator                                               |    |

|   | 7.2.1. | 1                                                              |    |

|   | 7.2.1. | I I                                                            |    |

|   | 7.2.1. | · · · · · · · · · · · · · · · · · · ·                          |    |

|   | 7.2.1. | -1                                                             |    |

|   | 7.2.1. | 51 1                                                           |    |

|   | 7.3 RF |                                                                | /4 |

| 8 | SYSTE  | M HINTS                                                        | 76 |

|   | 8.1 CA | LYPSO POWER BALLS ASSIGNMENT                                   |    |

|   | 8.1.1  | Recommended chips placement and filtering rules                |    |

|   | 8.1.2  | Capacitors Value recommendation                                |    |

|   | 8.1.2. |                                                                |    |

|   | 8.1.2. | 2 Calypso Power Supply                                         | 78 |

| 9 | APPEN  | DIX                                                            | 79 |

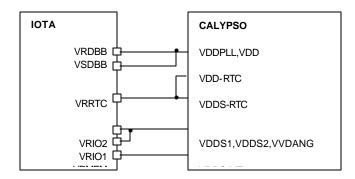

|   | 9.1 CO | NNECTION SCHEMATIC NAUSICA CALYPSO                             | 79 |

|   | 9.2 PO | WER SUPPLY CONNECTIONS BETWEEN NAUSICA/IOTA AND ULYSSE/CALYPSO | 80 |

**TI – Proprietary Information –**

PAGE: 4/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

## List of Tables

| Table 2-1 Calypso to Clara connections                                                          | 10       |

|-------------------------------------------------------------------------------------------------|----------|

| Table 2-2 lota to Clara connections                                                             | 10       |

| Table 2-3 Calypso to lota connections                                                           | 12       |

| Table 5-1SLEEP OFF Timing descriptions                                                          | 38       |

| Table 5-2 SLEEP ON timing description                                                           | 41       |

| Table 6-1 Estimated System BACKUP current consumption on BB                                     | 44       |

| Table 6-2 Estimated System BACKUP current consumption on MB                                     | 44       |

| Table 6-3 Estimated System OFF current consumption on MB                                        | 45       |

| Table 6-4 Estimated System SLEEP current consumption on MB                                      | 47       |

| Table 7-1 Electrical characteristics under normal operating conditions                          | 48       |

| Table 7-2 Electrical characteristics under normal operating conditions                          | 49       |

| Table 7-3 Electrical characteristics under normal operating conditions                          | 49       |

| Table 7-4 Electrical characteristics under normal operating conditions                          | 49       |

| Table 7-5 Electrical characteristics under normal operating conditions                          | 50       |

| Table 7-6 Electrical characteristics under normal operating conditions                          | 50       |

| Table 7-7 Electrical characteristics under normal operating conditions                          | 50       |

| Table 7-8 Electrical characteristics under normal operating conditions                          | 51       |

| Table 7-9 System BACKUP current consumption on BB                                               | 54       |

| Table 7-10 Precharge current vs VBAT                                                            | 62       |

| Table 7-11 LEDx Input characteristics                                                           | 65       |

| Table 7-12         Current resistance value versus register contents(Calypso C05).              | 70       |

| Table 7-13 External components general informations                                             | 71       |

| Table 7-14 Typical parameters value measured on market available crystals                       | 72       |

| Table 8-1 Ground connections                                                                    | 76       |

| Table 8-2 lota capacitors values                                                                | 78       |

| Table 8-3 Calypso capacitors values                                                             | 78       |

| List of figuros                                                                                 |          |

| List of figures                                                                                 | 10       |

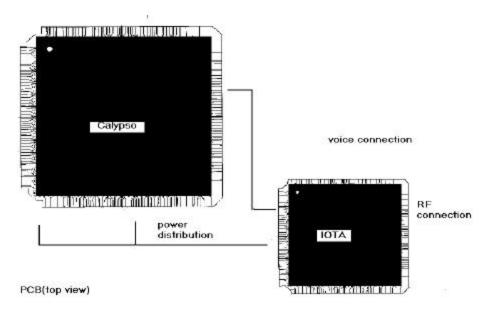

| Figure 2-1 System connections                                                                   | 10       |

| Figure 2-2 lota to Calypso supply connections                                                   | 17<br>19 |

| Figure 2-3 Calypso Power domains                                                                | 21       |

| Figure 3-1 Power Split supply connections                                                       | 21       |

| Figure 3-2 RESPWONZ signal behavior at first power up                                           | 22       |

| Figure 4-1 LDO BG reference during SLEEP mode<br>Figure 5-1 System operating modes transitions  | 23       |

| Figure 5-2 lota BBSWITCH and VRPC State Machine                                                 | 29       |

| Figure 5-4 SLEEP ON transition                                                                  | 41       |

| Figure 6-1 Active blocks in backup mode                                                         | 41       |

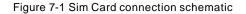

| Figure 7-1 Sim Card connection schematic                                                        | 44 48    |

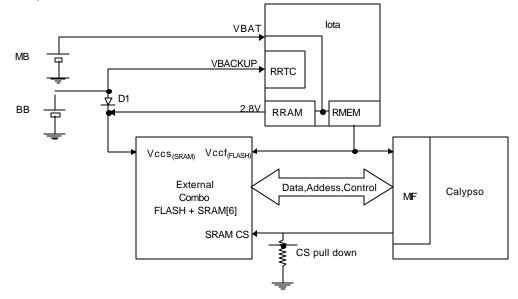

| Figure 7-2 Optimized Back-Up scheme connections                                                 | 40<br>52 |

| Figure 7-3 RRAM inverse current protection in OFF mode                                          | 53       |

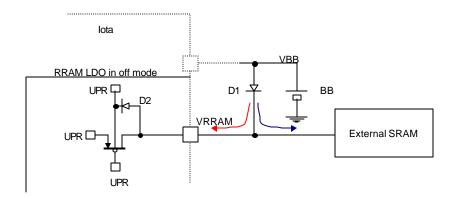

| Figure 7-4 UPR supply dependency on MB and BB                                                   | 53       |

| Figure 7-5 BCI block schematic and external component.                                          | 56       |

| Figure 7-6 BCI connections schematic and precharge current path                                 | 61       |

| Figure 7-7 Led drivers application schematic                                                    | 65       |

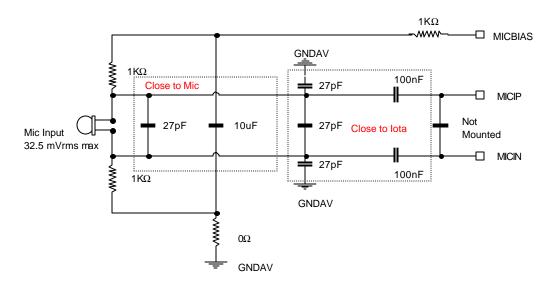

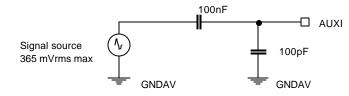

| Figure 7-8 Microphone schematic connections                                                     | 66       |

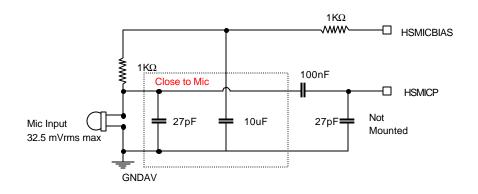

| Figure 7-9 Headset Microphone schematic connections                                             | 66       |

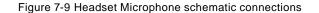

| Figure 7-10 Auxiliary input connections schematic                                               | 67       |

| Figure 7-11 Ear Output connections schematic                                                    | 67       |

| Figure 7-12 Headset Output connection schematic                                                 |          |

|                                                                                                 |          |

|                                                                                                 | 67       |

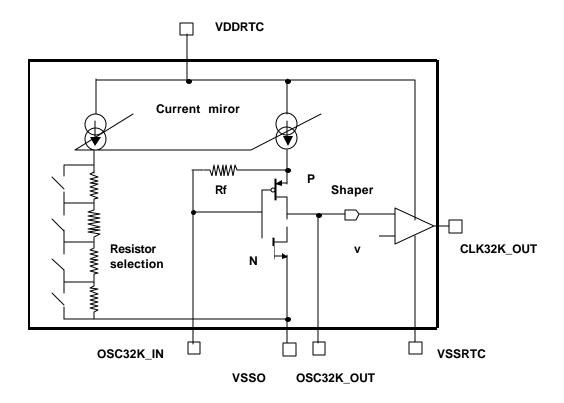

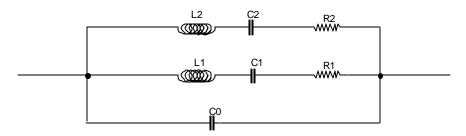

| Figure 7-13 Auxiliary Output schematic connections<br>Figure 7-14 Internal equivalent schematic |          |

**TI – Proprietary Information –**

PAGE: 5/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

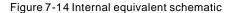

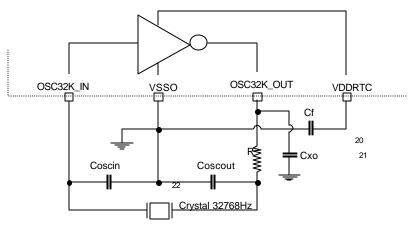

| Figure 7-15 External Components                                    | 71 |

|--------------------------------------------------------------------|----|

| Figure 7-16 Equivalent resonant circuit                            | 72 |

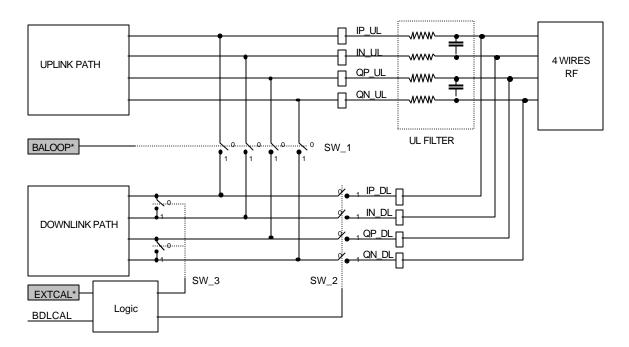

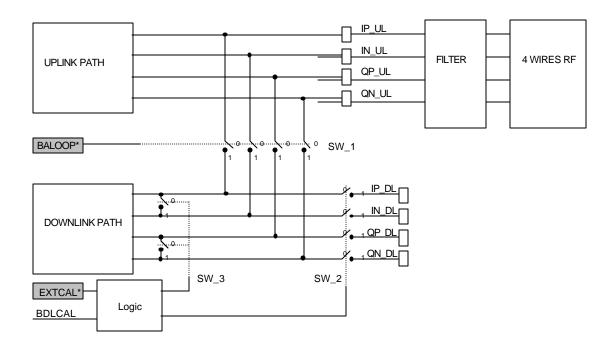

| Figure 7-17 Four wires RF connections to lota, Solution1           | 74 |

| Figure 7-18 Four wires RF connections to lota, Solution2           | 75 |

| Figure 8-1 Recommended Chip placement                              | 77 |

| Figure 8-2 Capacitor placing                                       | 77 |

| Figure 9-1 Calypso to Nausica connection schematic for split power | 79 |

| Figure 9-2 ABB to DBB supply connections                           | 80 |

## **TI** – Proprietary Information –

PAGE: 6/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

## **Reference documents:**

| [1] TWL3014          | IOTA Data Manual SWRS010             |          |         |

|----------------------|--------------------------------------|----------|---------|

| [2] TRF6150          | CLARA Specification                  |          | ver 2.5 |

| [3] HERCROM400G2     | CALYPSO Specification CAL000 ve      | er 0.5   |         |

| [4] ULYS015          | Ultra Low Power Down Controller ve   | er 1.1   |         |

| [5] ULYS002          | Activity control management          |          | ver 1.1 |

| [6] MB84VD2108/9X-85 | Stacked MCP Flash memory and SRAM sp | pecifica | tions   |

## Glossary:

| ABB       | Analog Base Band                                                                          |

|-----------|-------------------------------------------------------------------------------------------|

| DBB       | Digital Base Band                                                                         |

| LMM       | Lead Mega Module                                                                          |

| SM        | State Machine                                                                             |

| MB        | Main Battery                                                                              |

| BB        | Back-up Battery                                                                           |

| BG        | Band Gap                                                                                  |

| ACTIVMCLK | This bit at logical 1 indicates to the ABB that a stable 13Mhz is available to the system |

**TI – Proprietary Information –**

PAGE: 7/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

# 1 Introduction

Scope of this specification is to give a system point of view of TI GSM chipset solution . This specification will cover application aspect of a GSM system based on the three TI chips Calypso, lota, Clara that build up the TI GSM chipset solution.

## 1.1 Calypso

HERCROM 400G2 [3] is a chip implementing the digital base-band processes of a GSM/GPRS mobile phone. This chip combines a DSP sub-chip (LEAD2 CPU) with its program and data memories, a Micro-Controller core with emulation facilities (ARM7TDMIE), internal 8Kb of Boot ROM memory, 4M bit SRAM memory, a clock squarer cell, several compiled single-port or 2-ports RAM and CMOS gates.

The application of this circuit is the management of the GSM/GPRS base-band processes through the GSM layer 1, 2 and 3 protocols as described in the ETSI standard with a specific attention to the power consumption in both GSM dedicated and idle modes, and GPRS (class 12) capability.

## 1.2 lota

TWL3014 chip [1] includes a complete set of baseband functions to perform the interface and processing of voice signals, interface and processing of baseband in-phase (I) and quadrature (Q) signals which support single-slot and multi-slot mode, associated auxiliary RF control features, supply voltage regulation, battery charging control and switch ON/OFF system analysis.

## 1.3 Clara

The TRF6150 [2] is a triple band transceiver IC suitable for GSM, DCS and PCS GPRS class 12 applications.

The chip integrates:

- the receiver based on direct conversion architecture,

- the transmitter based on the modulation loop architecture,

- the frequency synthesis including an auxiliary N-integer synthesizer,

- a main N-fractional synthesizer,

- an IF VCO and RF VCO,

- the voltage regulators to supply on chip and off chip RF functions

- a power amplifier controller.

Few external components are required for a dual band application as a power amplifier, a switchplexer, only one dual band VCO and two front end filters.

**TI** – Proprietary Information –

PAGE: 8/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

# 2 System connections

TI – Proprietary Information –

PAGE: 9/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

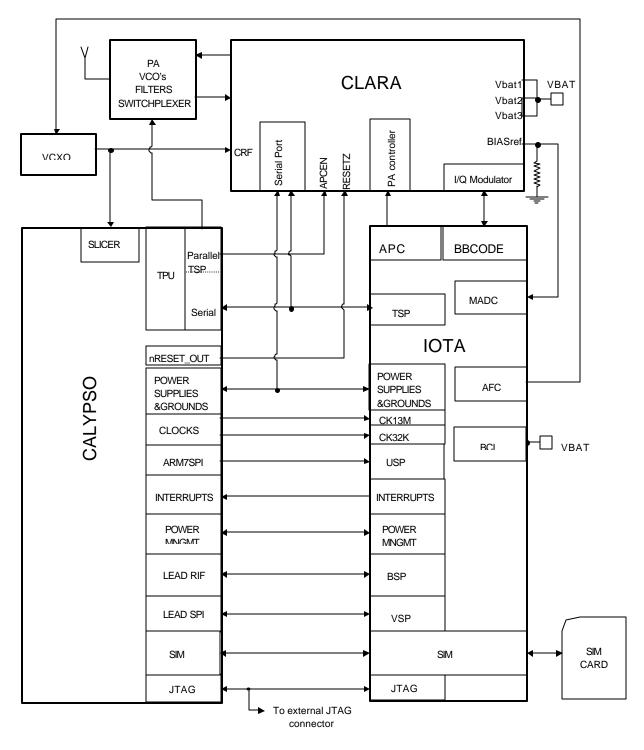

#### Figure 2-1 System connections

## 2.1 Calypso to Clara

Table 2-1 Calypso to Clara connections

| CALYPSO                 |        |      | CLARA    |        |      | Comments                      |

|-------------------------|--------|------|----------|--------|------|-------------------------------|

| Pin Name                | Pin nb | Ball | Pin Name | Pin nb | Ball |                               |

| nRESET_OUT              | 45     | N2   | RESETZ   | 17     | -    | Serial port register reset    |

| TSPDO                   | 109    | H11  | DAT      | 12     | -    | TSP serial interface to Clara |

| TSPEN(1) <sup>1</sup>   | 111    | H12  | EN       | 13     | -    | TSP serial interface to Clara |

| TSPCLKX                 | 107    | J14  | CLK      | 11     |      | TSP serial interface to Clara |

| TSPACT(11) <sup>2</sup> | 106    | J13  | APCEN    | 9      | -    | APC Enable signal             |

WARNING: Pin number and ball reference may not be updated. Please refer to latest spec version of Calypso and Clara

Calypso to Clara connections consist in few signals mainly dedicated to serial programmation of the Clara chip through the TSP. The TSP port is controlled by the TPU hence Clara register programmation is executed synchronously to the GSM time-base with a resolution of a GSM quarter of bit. For Clara register, data format and serial interface programming refer to CLA000 specification [2].

Also Clara serial interface reset is controlled by the Calypso reset signal for external peripheral and a TSPACT signal, generated by the parallel part of the TSP, provides an APC enable signal required by Clara with a GSM quarter bit resolution.

## 2.2 lota to Clara

Table 2-2 lota to Clara connections

| IOTA     |        |      | CLARA    |        |      | Comments                          |

|----------|--------|------|----------|--------|------|-----------------------------------|

| Pin Name | Pin nb | Ball | Pin Name | Pin nb | Ball |                                   |

| BULQM    | 73     | C9   | QN       | 18     | -    | I/Q UL&DL signals <sup>3 4</sup>  |

| BULQP    | 72     | C10  | QP       | 19     | -    | I/Q UL&DL signals                 |

| BULIM    | 69     | D10  | IN       | 20     | -    | I/Q UL&DL signals                 |

| BULIP    | 70     | D9   | IP       | 21     | -    | I/Q UL&DL signals                 |

| APC      | 32     | K4   | APC      | 8      | -    | PA envelope signal                |

| VRIO2    | 2      | B1   | VR4in    | 10     | -    | Serial interface supply voltage   |

| ADIN3    | 83     | C7   | BIASref  | 31     | -    | External current setting resistor |

| VBAT 94  | 94     | 0.4  | Vbat1    | 50     | -    | Reg1 battery supply voltage       |

| VDAT     | 94     | A4   | Vbat2    | 6      | -    | Reg2 battery supply voltage       |

|          |        |      | Vbat3    | 61     | -    | Reg3 battery supply voltage       |

WARNING: Pin number and ball reference may not be updated. Please refer to latest spec version of lota and Clara

lota to Clara connections include the I/Q Uplink and Downlink signals, the Automatic Power Control signal, the temperature sensor signal, serial interface supply connection and battery supply voltage connection.

The APC signal of lota APC module is used by the CLARA PA controller to generate a smooth PA control signal. Shapes, delays and levels for this signal are managed by DBB through the programmation of APC module.

<sup>3</sup> Direct connection is done between the four wires lota UL path and Clara UL/DL path.

<sup>4</sup> UL to DL path switch must be implemented in SW

TI – Proprietary Information –

PAGE: 10/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

<sup>&</sup>lt;sup>1</sup> Choice of TSPEN(x) can be done in order to ease PCB connections

$<sup>^{2}</sup>$  Choice of TSPACT(x) can be done in order to ease PCB connections

The VRIO signal is the lota power supply regulator output for IO's. It supplies the CLARA serial interface IO's as the CALYPSO TSP IO's in order to have serial connection on the same supply domain.

The ADIN3 to BIASref connection allows RF chip temperature measurements.

The VBAT connections is not an effective lota to Clara connection as the battery pack is external, it has been added to this table to highlight the fact that Clara regulators are directly linked to the Main Battery.

**TI** – Proprietary Information –

PAGE: 11/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

## 2.3 Calypso to lota

Table 2-3 Calypso to lota connections

| CALYPSO                  |                 | IOTA |          |        | Comments |                                        |

|--------------------------|-----------------|------|----------|--------|----------|----------------------------------------|

| Pin Name                 | Pin nb          | Ball | Pin Name | Pin nb | Ball     |                                        |

| TSP Serial interfa       | ace             |      | •        |        |          |                                        |

| TSPDO                    | 109             | H11  | TDR      | 21     | G3       |                                        |

| TSPEN(0)                 | 110             | H13  | TEN      | 22     | H1       |                                        |

| <b>RIF/BSP</b> Serial in | nterface        |      | •        |        |          |                                        |

| BFSR                     | 86              | L11  | BFSX     | 27     | K2       |                                        |

| BDR                      | 82              | K10  | BDX      | 26     | J1       |                                        |

| BFSX                     | 87              | P12  | BFSR     | 29     | H3       |                                        |

| BDX                      | 85              | M11  | BDR      | 28     | J3       |                                        |

| ARM SPI/USP Se           | erial Interface |      | •        |        |          |                                        |

| MCUDI                    | 66              | N7   | UDX      | 35     | J5       | Tristate when not enabled <sup>5</sup> |

| MCUDO                    | 67              | M7   | UDR      | 34     | K5       |                                        |

| MCUEN(0)                 | 68              | M8   | UEN      | 39     | K6       |                                        |

| LEAD SPI/VSP             |                 |      | •        |        |          |                                        |

| VCLKRX                   | 88              | N12  | VCK      | 30     | K3       |                                        |

| VDX                      | 91              | P14  | VDR      | 41     | H5       |                                        |

| VDR                      | 90              | N13  | VDX      | 37     | F5       |                                        |

| VFSRX                    | 92              | M13  | VFS      | 36     | G5       |                                        |

| SIM Interface            |                 |      | •        |        |          |                                        |

| SIM_CLK                  | 119             | F13  | DBBSCK   | 17     | F4       |                                        |

| SIM_IO                   | 115             | G13  | DBBSIO   | 13     | E5       |                                        |

| SIM_RST                  | 117             | G10  | DBBSRST  | 18     | G4       |                                        |

| JTAG Interface           | -               |      |          |        |          |                                        |

| TDO                      | 147             | C10  | TDI      | 68     | D7       |                                        |

| TMS                      | 148             | E9   | TMS      | 66     | E8       | Ext connection to JTAG controller      |

| TCK                      | 145             | B10  | TCK      | 71     | D8       | Ext connection to JTAG controller      |

| TDI                      | 144             | D10  |          |        |          | Ext connection to JTAG controller      |

|                          |                 |      | TDO      | 67     | E7       | Ext connection to JTAG controller      |

| CLOCKS                   |                 |      |          |        |          |                                        |

| CLK32K_OUT               | 132             | C12  | CK32K    | 10     | E2       |                                        |

| CLK13M_OUT               | 120             | F12  | CK13M    | 12     | E4       |                                        |

| INTERRUPTS               | ·               | •    |          |        | •        |                                        |

| EXT_IRQ                  | 42              | M3   | INT2     | 88     | E6       |                                        |

| EXT_FIQ                  | 44              | P1   | INT1     | 41     | H6       |                                        |

| POWER MGMT               | ·               |      | •        |        |          |                                        |

| ITWAKEUP                 | 131             | B14  | ITWAKEUP | 6      | D2       |                                        |

| ON_OFF                   | 126             | F10  | ONNOFF   | 11     | E3       |                                        |

| RESPWRONZ                | 129             | D12  | RESPWONZ | 8      | D3       |                                        |

WARNING: Pin number and ball reference may not be updated. Please refer to latest spec version of Calypso and lota

<sup>5</sup> To avoid current consumption a pull down must be added on this line.

**TI – Proprietary Information –**

PAGE: 12/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

| CALYPSO        |        |      | IOTA      |        |      | Comments |

|----------------|--------|------|-----------|--------|------|----------|

| Pin Name       | Pin nb | Ball | Pin Name  | Pin nb | Ball |          |

| POWER SUPPLIES | 5      |      |           |        |      |          |

|                | 13     | E1   |           | 24     | J1   |          |

|                | 40     | M1   | VRDBB     |        |      |          |

| VDD            | 65     | P7   | Sense on  |        |      |          |

| VDD            | 94     | N14  | VSDBB     | 23     | H2   |          |

|                | 137    | B12  |           |        |      |          |

|                | 169    | A5   |           |        |      |          |

| VDD-RTC        | 127    | D14  | VRRTC     | 7      | D1   |          |

| VDDS-RTC       | 128    | D13  | VRRTC     | 7      | D1   |          |

|                | 8      | D1   |           | 19     | G1   |          |

| VDDS-MIF       | 22     | G1   | VRMEM     |        |      |          |

| VDDS-IVIIF     | 164    | B6   | VRIVIEIVI |        |      |          |

|                | 173    | A4   |           |        |      |          |

|                | 55     | N5   | VRIO2     | 2      | B1   |          |

| VDDS1          | 98     | L14  | Sense on  |        |      |          |

| VDDS2          | 142    | A11  | VRIO1     | 1      | B2   |          |

| VDDPLL         | 121    | F11  | VRDBB     | 24     | J1   |          |

| VDDANG         | 125    | E11  | VRIO2     | 2      | B1   |          |

WARNING: Pin number and ball reference may not be updated. Please refer to latest spec version of Calypso and lota

#### 2.3.1 TSP serial interface

The TSP serial interface allows the serial transmission of baseband control windows for the lota BBCODEC. It is managed through a TPU scenario hence it allows GSM quarter bit resolution and a precise positioning of CODEC commands among the GSM TDMA frame.

Data format for this transmission is seven bits including UL/DL commands (On, Calibrate, Enable) and a start bit for ADC conversion. This command bit allows to place at precise moments in the TDMA frame the start of the ADC conversion.

lota register are not accessible through this serial link, sense of transmission is from Calypso to lota only.

Clara serial interface is also connected to Calypso TSP. Through this link the Calypso device programs Clara register in order to control regulators, synthesizers, the receiver, the offset PLL and the P.A. controller.

TSP serial clock runs at 6.5MHz.

#### 2.3.2 RIF/BSP se rial interface

This interface is dedicated to the UL and DL transmission of I/Q samples between the DSP and the BBCODEC and to lota register access.

On the UL path the DSP sends to the CODEC the burst bits to be modulated while on the DL path it receives non demodulated I/Q samples.

Write access to lota register is done using the same data format as the UL. Main functions executed are:

- APC parameters programmation (levels, delays, ramp coefficients)

- AFC

- Voice CODEC control

No lota read accesses are performed in current SW implementation through this interface. Register accesses could be considered synchronized to the TDMA frame as the DSP receives commands on TDMA frame start boundary.

**TI – Proprietary Information –**

PAGE: 13/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

Clock frequency of RIF/BSP serial link is 13 MHz. BSP access are not allowed when ACTIVMCLK='0'.

## 2.3.3 ARM SPI/USP serial interface

This interface is dedicated to lota read and write register accesses from Calypso. Through this link is possible to access all lota register, hence this port is used to configure and to manage the status of each block of lota device. Also ADC result of conversion can be read through this interface. This access is asynchronous to the TDMA frame and has a higher priority than the BSP access. Possible conflicts due to simultaneous access from ARM SPI and LEAD RIF are managed by the lota IBIC. This serial link runs at 13 MHz.

## 2.3.4 LEAD SPI/VSP serial interface

This interface allows voice samples exchanges in DL and UL direction between the DSP and the lota Voice Band CODEC. lota VSP is the master port in the transmission, serial link runs at 500 kHz.

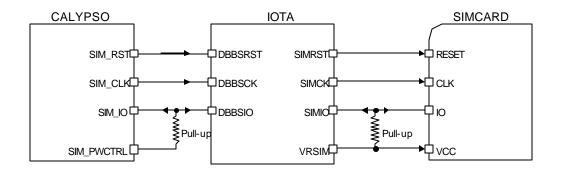

## 2.3.5 SIM interface

The Sim Card digital interface in ABB insures the translation of logic levels between DBB and Sim Card, for the transmission of 3 different signals:

- A clock derived from a clock elaborated in DBB, to the Sim-Card (DBBSCK ⇔ SIM\_CK)

- A reset signal from DBB to the Sim Card (DBBSRST ⇒ SIM\_RST),

- A serial data from DBB to the Sim Card (DBBSIO ⇔ SIM\_IO) and vice-versa.

The SIM card interface can be programmed to drive a 1.8V or 3V Sim Card.

## 2.3.6 JTAG interface

The test access port (TAP) meets JTAG testability standard (IEEE Std1131.1-1990). TAP allows public instructions set of JTAG standard and also private instructions to configure the device in special modes for test or debug purpose.

## 2.3.7 CLOCKS

lota device receives two clocks from Calypso:

- A slow clock CLK32K\_OUT used by the DBB as reference clock for low power modes (back-up, deep-sleep).

The ABB adopt this clock as the VRPC synchronous state machine clock and as reference clock when fast clock is not present.

- A fast clock CLK13M\_OUT used by the DBB and ABB as reference clock for all modules including serial transmission<sup>6</sup>.

<sup>&</sup>lt;sup>6</sup> This means that a single fast clock signal only goes from DBB to ABB. All serial interfaces adopt this clock as reference clock, no need to include a clock signal in each port connection.

TI – Proprietary Information –

PAGE: 14/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

## 2.3.8 INTERRUPTS

lota device is able to generate two kinds of interrupts:

- An emergency interrupt connected to Calypso EXT\_FIQ signaling the detection of a low battery voltage.

- An event detection interrupt connected to Calypso EXT\_IRQ signaling :

- Falling or rising edge at RPWON pin.

- Falling edge at PWON pin.

- Termination of an analog to digital conversion.

- Charger plug.

#### 2.3.9 POWER MGMNT

Those three signals controls system status and system status transitions, they are supplied on the VRRTC power domain.

The nRESPWONZ signal is generated by the ABB, it is the reset of the power split part of the DBB chip. It is active only one time (as long any kind of supply, BB or MB is present) at the first start of the mobile. Split power logic will provide to propagate this signal as global reset as soon as power supply will be present on the rest of the chip.

The ON\_nOFF signal is generated by the ABB, it is the ASIC modules, ARM, LMM, reset. It is at logical low level each time the system is switched off. Also this signal is managed by the split power logic and propagated to the rest of the circuit.

High logical level is asserted on this signal when the lota power management has completed the enabling sequence of all LDO's meaning that the system is correctly supplied and that SW can be correctly executed.

At this time the MCU SW starts from its reset state.

The ITWAKEUP signal is generated by the DBB and it is used to wake up the system from low power modes (backup, deep sleep). It is built as a combination of all the interrupt request that are allowed to awake the Calypso ULPD module and the RTC alarm.

**TI** – Proprietary Information –

PAGE: 15/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

**TI** – Proprietary Information –

PAGE: 16/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

reserved for ABB private use only

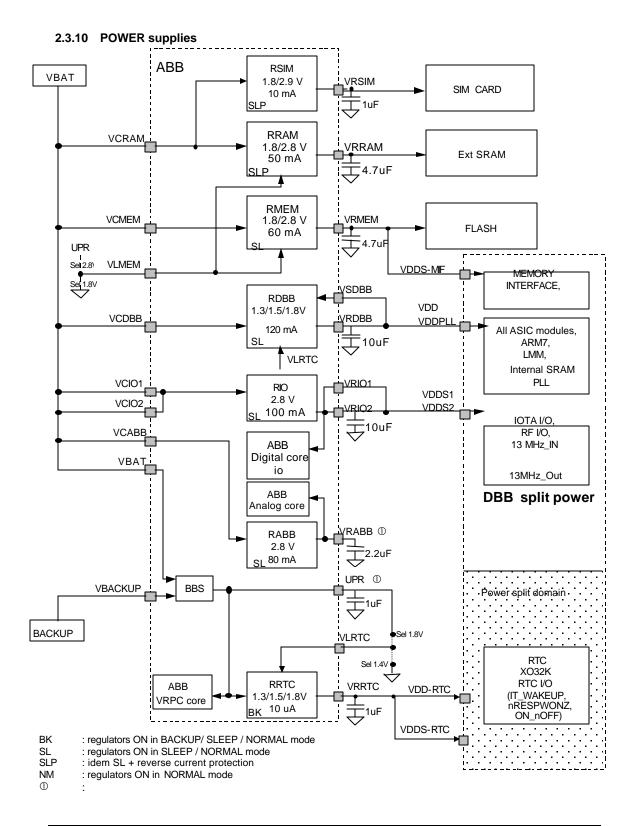

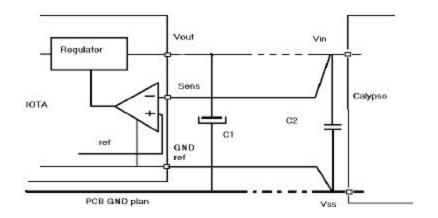

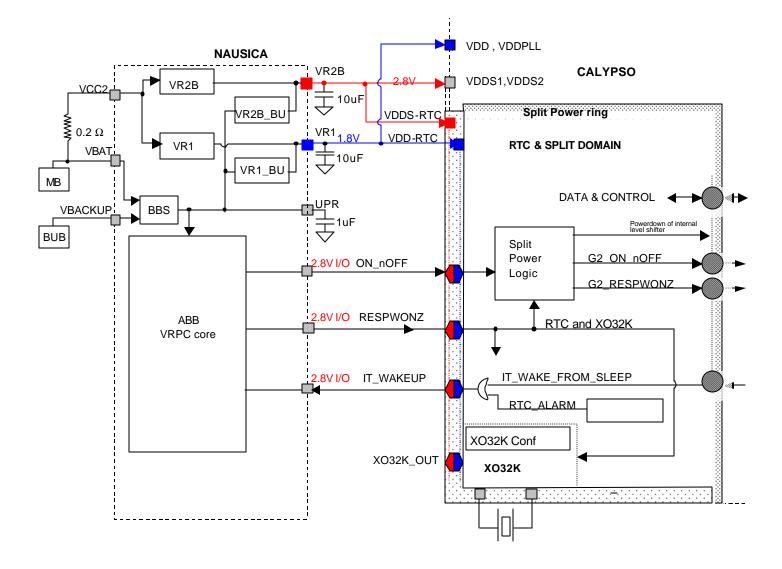

Figure 2-2 lota to Calypso supply connections

**TI** – Proprietary Information –

PAGE: 17/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

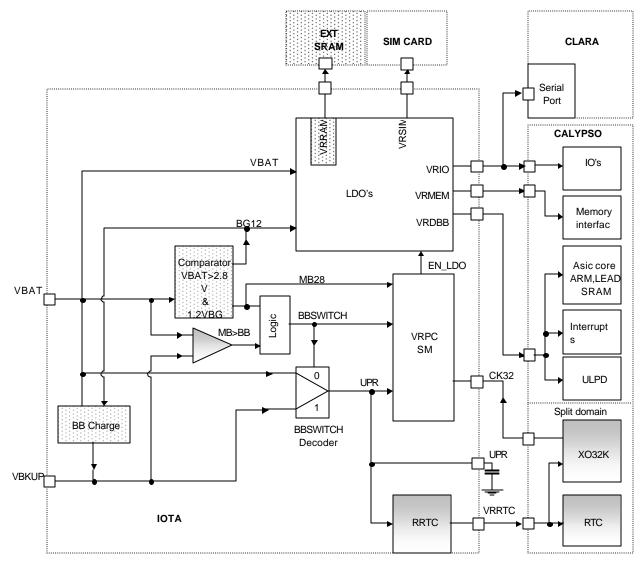

The schematic above shows lota to Calypso power supply connections. Items to be highlighted on that schematic are the following:

- All main regulators have as non-regulated input the VBAT pin. Hence while MB is not connected no supply will be provided at the output of those LDO's.

- The back up regulator RRTC has as non-regulated input either the MB or BB, it is always enabled and provides supply to the Calypso "power split" domain on every functional mode of the system.

- Default voltage value for both RRTC and RDBB can be selected between 1.5V and 1.8V through the VLRTC input pin.

- Default voltage value of RMEM can be selected between 2.8V and 1.8V through the VLMEM input pin.

- RDBB regulator allows external voltage sensing for sharper regulation on the VSDBB input pin. This allows to eliminate of the pad and wire connection drop to the Calypso power supply input. To make this feature effective, return sense point must be chosen as next as possible to Calypso input.

- In lota to Calypso application RTC I/O's level shifters are used with same voltage value at both sides => VDD-RTC = VDDS-RTC = 1.8V.

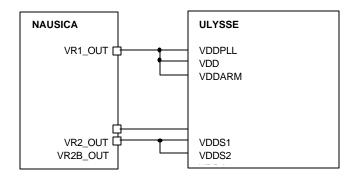

#### 2.3.11 Calypso Supplies voltages rules

The Calypso device has five different Power domains corresponding to the following IOTA supplies:

| A : RTC core domain | => RRTC     | 1.5V – 1.8V depending on VLRTC connection |

|---------------------|-------------|-------------------------------------------|

| B: ASIC core domain | => RDBB     | 1.5V – 1.8V depending on VLMEM connection |

| C: RTC I/O domain   | => RRTC     | 1.5V – 1.8V depending on VLRTC connection |

| D: ASIC I/O domain  | => RIO 2.8V |                                           |

| E: Memory interface | => RMEM     | 1.8V – 2.8V depending on VLMEM connection |

PAGE: 18/81

Strictly Private

**TI** – Proprietary Information –

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

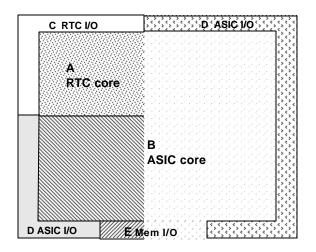

Figure 2-3 Calypso Power domains

# To avoid current leakage at the interface A B the supply voltage of A domain must always be higher or equal to the B domain one.

For that reason the VLRTC input pin of IOTA is used to select the default-regulated voltage of both RRTC and RDBB regulators.

Also user SW must take care of never break the above rule, as the RRTC and RDBB output voltage values could be independently selected by SW.

**TI** – Proprietary Information –

PAGE: 19/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

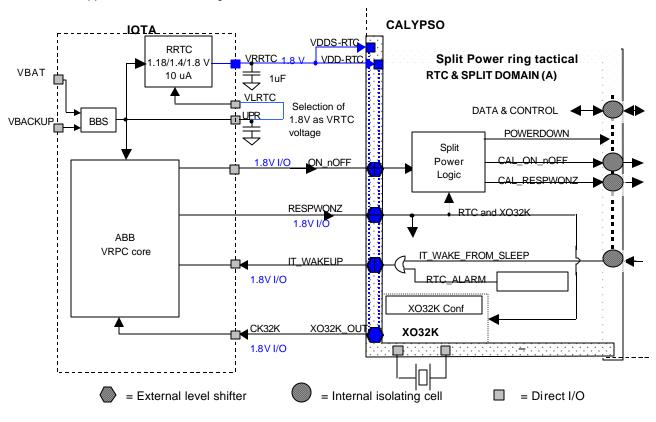

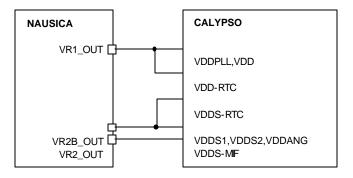

# 3 Power split concept in Calypso-lota systems

To have a minimum of consumption during OFF state in mobile equipment, only the active logic elements have to be supplied. Those blocks in a mobile application are the RTC (Real Time Clock) module, the XO32K (32 kHz os cillator) module and the INTH (Interrupt Handler) for the DBB part and the POR (Power On Reset) logic and a dedicated LDO in the ABB part.

This approach is possible by using Calypso Split Power feature together with the lota dedicated regulator VRRTC.

In Calypso the core power domain is split in two sub domains powered with different voltage supplies. Those two domains can be selectively powered allowing the shut down of all those blocks not involved in OFF state logic functions.

Tactical cells realize the separation between the un-supplied part of the core and the active domain in order to avoid any current leakage between supply domains.

A POWERDOWN signal generated by the split control logic allows the isolation of the RTC and split domain from the rest of the circuit. This signal is active when the ON\_nOFF signal coming from lota is at low level indicating that main regulators are disabled.

The RESPWONZ signal is used to reset the RTC, the Split power logic and the XO32K module. The external interface of split domains adopts level shifter I/O's this to allow compatibility with Nausica device. Note that in lota/Calypso systems this feature is not used because split core is supplied at the same voltage of external I/O's

**TI – Proprietary Information –**

PAGE: 20/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

Figure 3-1 Power Split supply connections

**TI – Proprietary Information –**

PAGE: 21/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

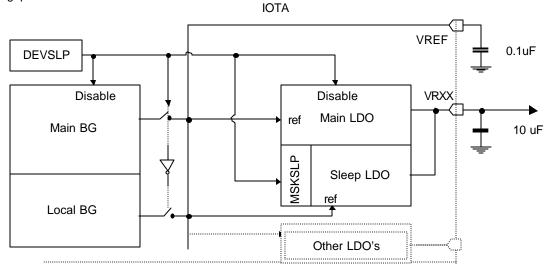

lota device dedicates a special low consumption LDO RRTC for split domain only. This LDO supplies:

- The VRPC digital core

- The power management I/O of lota and Calypso split domain

- The split supply core (RTC and XO32K)

This regulator is always enabled and has a limited current drive capability(30uA). Hence as soon as a MB or a BB battery are connected to lota the VRRTC regulator will provide supply to the 32K oscillator and to the RTC.

## 3.1 System Power On Reset generation

The RESPWONZ signal is used as reset for the lota VRPC SM and for Calypso RTC, Split power logic and the XO32K module.

The nRESPWONZ signal is held in a low state until both conditions below are not matched:

- The VRRTC regulator is at the nominal regulated voltage.

- The UPR voltage is higher than 2.6V

This to allow internal digital VRPC logic reset and external RTC and XO32K modules reset. Once this signal has been released the XO32K modules starts providing the OSC32K\_OUT signal to lota. This clock is used by the VRPC synchronous state machine.

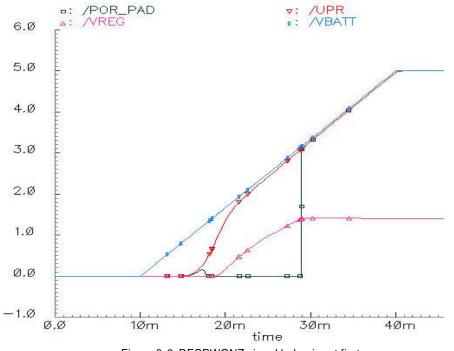

Simulation diagram below illustrate the nRESPWONZ signal logic behavior (POR\_PAD in the plot) related to the VRRTC output voltage (VREG in the plot).

Figure 3-2 RESPWONZ signal behavior at first power up

**TI – Proprietary Information –**

PAGE: 22/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

Simulation conditions are :

- 1uF on VRRTC\_OUT

- 10 uF on UPR

- rise time of the battery from 0V to 5V 30 ms.

In this example the nRESPWONZ signal is released only when the VRRTC regulator has reached its nominal voltage. Correct reset of the split part of Calypso is effective when split core is supplied with 80% of the nominal voltage and nRESPWONZ signal is held low for at least 5 ns. This is the case in the diagram above.

For what concern decreasing value of UPR the nRESPWONZ signal is forced to logic zero when the UPR voltage goes below 2.1V. This will reset the whole system.

**TI** – Proprietary Information –

PAGE: 23/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

# 4 System modes

In the following paragraphs are illustrated the different operating modes of the mobile. First objective of this analysis is to define the modes and to state which are the working blocks on each of them. Next chapters then, will consider system transitions between operating modes and current consumption evaluation of the system in most of them.

## 4.1 No Supply

This mode is characterized by the lack of supply sources neither from MB nor from BB. It can be the case of missing batteries or flat batteries. All ABB register are in reset state, DBB is forced to reset.

## 4.2 Active

Activity of the system is tightly linked to the state of the voltage regulators that provide current. Two chips, in the proposed chipset solution, have embedded regulators: lota and Clara While in Clara device LDO's are exclusively dedicated to the RF part of the system and their enable is related to RF periods of activity, lota ones are used to supply both the DBB and the ABB part of the chipset. Thus any SW control activity on the system could be possible only when those regulators are active.

First definition of the active mode hence could be the following: System is in active mode when both lota and Clara LDO's are enabled and SW is able to manage GSM activity.

Once lota regulators are enabled and the Switch ON procedure terminated, SW becomes the system master ant it is its own choice to select operating modules depending on the application. MB values allowing the system to stay in active mode are MB > 2.8V

## 4.3 Off

This mode is characterized by the presence of a charged MB (MB > 3.2V) and by the disabled state of lota LDO's<sup>7</sup>. In this condition system is ready to accept a switch on command to pass in active mode. The ON\_nOFF signal is at low level indicating to the DBB that LDO's are not able to deliver nominal current and isolating the split domain from the rest of the Calypso chip. The system active blocks in this mode are:

## lota:

- VRRTC regulator

- POR logic

- BBSWITCH logic

- Power management I/O's (RESPWONZ, ON\_nOFF, IT\_WAKEUP)

- LDO's programmed to stay in SLEEP mode

## Calypso:

- RTC

- XO32K

- Power split Logic

- Split I/O

## Clara:

None

<sup>7</sup> In OFF state RDBB,RMEM,RRAM,RIO,RSIM and RABB could stay in Sleep mode if selected through the MSKOFF register. In this mode LDO's max deliverable current is 1 mA.

TI – Proprietary Information –

PAGE: 24/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

## 4.4 Backup

This mode is characterized by the fact that the supply source of the system is the BB or a MB below 3.2V. In this state only the minimal mobile functionality's are still alive, the real time clock RTC, the POR logic and on some architectures the SRAM backup supply. Any switch on command in this state will be ignored.

The ON\_nOFF signal is low, and the Calypso split domain isolated.

## 4.5 Sleep

System sleep mode is characterized by a low consumption state of lota regulators. Although still enabled lota LDO's are no longer able to provide the full active rated current. They keep the regulated voltage with a reduced maximum rated output current of 1mA.

This allows the system to freeze its configuration during inactivity periods.

In this mode in fact the ON\_nOFF signals stays at high logical level (no register reset is asserted) but application SW is no longer enabled to run. This mode has been expressly conceived for system current consumption reduction during inactive periods of mobile paging mode and to support the L1 Deep Sleep SW mode.

Also in Sleep mode lota main band gap is off, reference for regulators is provided by a local band gap.

Figure 4-1 LDO BG reference during SLEEP mode

In Sleep mode current consumption is limited to the consumption of the local bangap and of the sleep regulator. Advantage of this architecture is that the external capacitors on regulator outputs and on VREF pins keep the charge during sleep mode allowing a quick re-start of LDO and main bangap entering the active mode.

lota LDO's supporting the sleep feature are: RSIM, RRAM, RMEM, RDBB, RIO and RABB. By default the RABB LDO is set in off mode when the system enters the SLEEP mode, while all the others stay active in the low current consumption mode. Different behavior of LDO's could be configured through VRPCMSK register. Selected regulators (MSKSLP = 1) will be disabled entering in sleep mode.

**TI – Proprietary Information –**

PAGE: 25/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

Active blocks in this mode are:

#### lota:

- VRRTC regulator

- POR logic

- Power management I/O's (RESPWONZ, ON\_nOFF, IT\_WAKEUP)

- MB vs BB comparator

- Sleep LDO's

- Local bandgap

- BB charge (if enabled)

## Calypso:

- RTC

- XO32K

- Power split Logic

- ULPD

- INTH

- All supply domains are powered but no current sink is allowed

## Clara:

Serial Port

## **TI – Proprietary Information –**

PAGE: 26/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

# 5 System transitions between operating modes

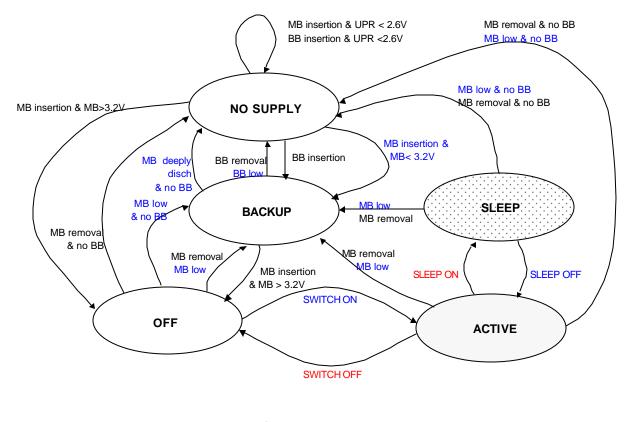

The flow chart below describes system states transitions and their driving events. Following paragraphs will detail driving events.

|                    | Fi                                                                   | gure 5-1 System operating modes transitions                                                                   |   |  |

|--------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---|--|

| NO SUPPLY          | UPR<2.6V, 0                                                          | $DN_nOFF = 0, nRESPWONZ = 0$                                                                                  |   |  |

| BACKUP             | UPR<3.2V, s                                                          | start conditions not accepted, ON_nOFF = 0, Calypso split isolated                                            |   |  |

| OFF                | UPR>3.2V, s                                                          | start condition accepted, ON_nOFF = 0                                                                         |   |  |

| ACTIVE             | UPR>2.8V <sup>8</sup> ,                                              | SW control of the system, $ON_nOFF = 1$                                                                       |   |  |

| In BLUE<br>In BLAC | characters<br>characters<br>K characters                             | : SW driven transitions<br>: HW detection driven transitions<br>: Supply insertion/removal driven transitions | Ð |  |

| A high lo          | A high logic level of the ON_nOFF signal characterizes shaded states |                                                                                                               |   |  |

<sup>8</sup>The system is designed to work correctly down to 3V battery value. In GSM application battery voltage is highly noised by the voltage drop induced by the PA (300-400 mV of battery drop during busrt emission).Hence GSM application SW decides to pass in OFF state long time before the battery voltage reaches 3V.

TI – Proprietary Information –

PAGE: 27/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

**TI – Proprietary Information –**

PAGE: 28/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

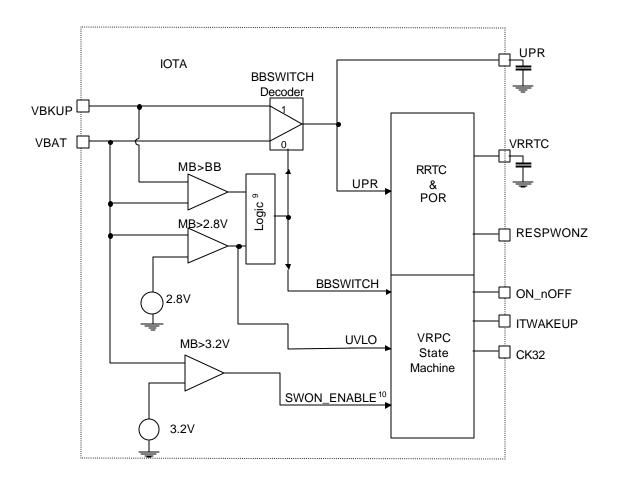

## 5.1 Supply insertion/removal driven transitions

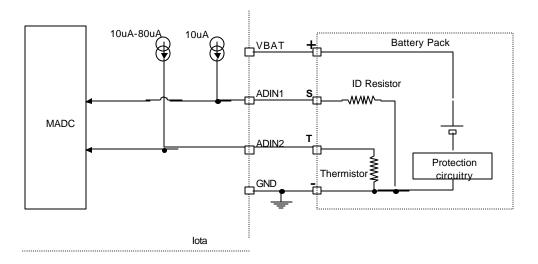

The lota device has a dedicated logic to manage system states depending on the presence of main and back up batteries. The VRPC state machine is able to detect MB and BB presence and their voltage level and to condition system behavior through the RESPWONZ and ON\_nOFF outputs. For design constraints when the system is conceived to work without BB the lota VBKUP pin must be connected to VBAT.

Description of the following transitions consider this connection present when no BB is used.

Figure 5-2 lota BBSWITCH and VRPC State Machine

<sup>10</sup> SWON\_ENABLE conditions VRPC SM switch on sequence to the voltage of MB. Only if MB>3.2V switch on is allowed.

**TI – Proprietary Information –**

PAGE: 29/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

<sup>&</sup>lt;sup>9</sup> BBSWITCH = 1 if MB<BB & MB<2.8V

#### 5.1.1 MB insertion

Three cases are possible:

System is not using BB (VBAT is connected to VBKUP) inserted battery is charged (MB> 3.2V).

MB insertion from a NO SUPPLY state produces a first start of mobile, a so-called POWER ON, and the mobile passes in OFF state.

The POR(Power On Reset) logic generates the RESPWON signal to reset internal VRPC logic and to Calypso split domain once the RRTC LDO has reached its nominal voltage. The VRPC state machine receives the 32K clock from Calypso XO32K supplied by the RRTC regulator and it is ready to accept a switch on conditions as MB value is higher than 3.2V(SWON\_ENABLE). The ON\_nOFF signal stays at low logical level indicating that no switch on condition has been detected.

The BBSWITCH signal assumes the low logical level allowing the UPR to be supplied by the  $\ensuremath{\mathsf{MB}}$

2) System is using BB but it is not present at a fully charged MB insertion.

This is an abnormal working configuration because VBKP pin must not be left floating. Nevertheless this configuration will not create problems as long as the MB is above 2.8V. For MB values below this threshold the BBSWITCH logic may become sensible to the VBCKUP floating input and generate some undesired switch of the MB/BB decoder. This will impact the UPR voltage compromising the whole behavior of the system.

3) BB present at MB>3.2V insertion.

The insertion of a charged MB will make the system pass from the BACKUP state to the OFF state. The BBSWITCH signal will keep the low logic level signaling to the BBSWITCH decoder to switch on MB and to the VRPC SM that is possible to accept switch on events. The signal ON\_nOFF stays at low level.

At the insertion of a MB the system will pass in OFF state if MB>3.2V as described for the three cases above or in BACKUP state if 2.6V<MB<3.2V. If MB<2.6V system stays in NO SUPPLY state.

## 5.1.2 BB insertion

Assuming that the system is in a NO SUPPLY mode and that BB is fully charged, the BB insertion generates the transition to the BACKUP mode.

As in the case of MB insertion from a NO SUPPLY condition this will generate a POWER ON of the system (first start). The POR (Power On Reset) logic generates the RESPWON signal to reset internal VRPC logic and to Calypso split domain once the RRTC LDO has reached its nominal voltage. The VRPC state machine receives the 32K clock from Calypso XO32K supplied by the RRTC regulator but it is not sensible to switch on events because SM inputs indicate that there is not MB. The signal ON\_nOFF stays at low level.

System stays in NO SUPPLY state if BB voltage is not enough to bring the UPR voltage above 2.6V.

**TI – Proprietary Information –**

PAGE: 30/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

## 5.1.3 MB removal

The MB removal will bring the system in one of the two states NO SUPPLY or BACKUP depending by the presence of a BB battery. Removing MB while the system is in SLEEP or ACTIVE state will make lota generate an INT1 to the DBB signaling that an EMERGENCY condition has occurred. The DBB is not able to treat this interrupt while in SLEEP mode.

This is possible only during active periods. From the interrupt generation the lota VRPC SM gives the system a 150 us<sup>11</sup> timeout after which all regulators (except RRTC) are disabled.

## 5.1.4 BB removal

Assuming the system in BACKUP mode BB removal bring the system in NO SUPPLY state.

## 5.2 HW driven transitions

HW driven transitions includes state changes due to detection of HW events, as BB or MB discharge below a given threshold, and switch on events. While the first are to be considered as a safety feature of the system preventing faulty SW execution due to sudden lack of supply and the over-discharge of the batteries latter are to be considered as state changes due to external stimulus (SWITCH ON) or system power management stimulus (SLEEP OFF)

## 5.2.1 MB low

The lota power management reacts to MB low condition depending on the system state in which this condition has been detected and on the presence/lack of a charged BB.

Also the condition "MB low" could be associated to different threshold values of the battery depending again on the system state.

MB low condition detected in:

#### OFF state

For this state the MB low condition consists in the detection of MB voltage under the 3.2V threshold (SWON ENABLE threshold).

The VRPC SM blocks switch on condition sensitivity and the system passes into BACKUP mode. Main regulators programmed to stay in sleep mode during OFF state remain enabled and still supplied on the MB.

## ACTIVE state

For this state the MB low condition consists in the detection of MB voltage under the 2.8V threshold (UVLO threshold).

## Charged BB present:

The UVLO comparator detects that MB voltage has undergone the 2.8V threshold. BBSWITCH signal is set to logic one because both conditions MB<2.8V & MB<BB are valid.

The VRPC SM :

- clears the MSKOFF register

- generates an INT1 signaling the EMERGENCY condition

- starts the 150 us watchdog timer.

At the end of the WD count

sets the ON\_nOFF signal to logic zero

<sup>11</sup> This value is strongly dependent on the amount of charge stored in LDO's external capacitors and on system consumption.

TI – Proprietary Information –

PAGE: 31/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

- disables LDO's using MSKOFF register (previously cleared => cuts all

- disables lota Band Gap.

In this configuration lota UPR line is powered on BB. System passes to BACKUP state.

During the Watchdog interval application SW has 150 us<sup>11</sup> corresponding to

1950 13MHz clock cycles to treat the INT1 and execute possible configuration accesses in order to enter the BACKUP state.

**No BB:** Same as above, the only differentiating factor is that BBSWITCH never passes to logic one thus UPR line is always supplied by the MB

## SLEEP state

Same as ACTIVE state. The SW does not take INT1 generation in account.

#### BAKUP state

For this state the MB low condition consists in the detection of MB voltage under the 2.8V threshold (UVLO threshold). Main regulators previously programmed to stay in sleep mode during OFF and BACKUP state remain enabled but they are no longer able to provide a regulated output. They will still sink current from MB following its decreasing value.

**Charged BB present:** BBSWITCH signal is set to logic one because both conditions MB<2.8V & MB<BB are valid. System stays in BACKUP state but UPR is now provided by the BB.

**No BB:** No action on BBSWITCH UPR is still supplied by MB, system stays in BACKUP.

#### 5.2.2 BB low

This event generate a system state transition to NO SUPPLY in the case system is in BACKUP state and MB is missing or deeply discharged.

Threshold BB low is fixed by the lota POR logic that assert a reset (nRESPWONZ to logic zero) when the UPR voltage goes below 2.1V. The system enters the NO SUPPLY state. In the case of a present MB and some enabled main LDO this reset will also disable still active regulators.

#### 5.2.3 MB deeply discharged & no BB

Same as above, when the MB discharge makes the UPR voltage going below 2.1V system passes from BACKUP state to NO SUPPLY state.

#### 5.2.4 SWITCH ON

Switch on is possible only when a charged MB powers the system. Battery voltage values allowing switch on transition are above 3.2V(SWON\_ENABLE input to the SM). There are four SWITCH ON events that allow the mobile to exit the OFF state and enter into ACTIVE state:

**TI – Proprietary Information –**

PAGE: 32/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

- Falling edge on the lota PWRON pin PWRON pin is connected externally to the ON/OFF keypad button and internally pulled up to the VBAT voltage domain through a resistor whose value may vary between 300 KΩ and 500 KΩ. Hence as soon VBAT goes high PWRON pin follows VBAT and assuming its inactive logical level. Button push generates the falling edge on PWRON pin. This input is de-bounced for 1034\*T<sub>32K</sub> time interval. If PWRON pin level is still low after the de-bouncing period the VRPC SM starts the SWITCH ON sequence. Note that at this stage no interrupt request is generated toward the DBB.

- Falling edge on the lota RPWRONZ pin.

RPWRON pin has exactly the same characteristics than the PWRON pin.

It is adopted to switch on the mobile through other events than a keypad ON/OFF This could be the case for an external accessory plug.

- Rising edge on ITWAKEUP pin

This is the case of a wake-up event generated by the RTC (Real Time Clock) module of

DBB. If a wake-up time has been programmed into the RTC registers this module

asserts a switch on event at the specified time wakening-up the system. This can be

the case of auto switch on application or alarm application.

- Voltage on CHG pin higher than the voltage on VBAT pin (charger insertion). This is the case of a charger insertion whose voltage is higher than the MB voltage allowing charging process.

If the system is fitted with a flat MB plug of the charger will generate a switch on condition only when the MB, thanks to the precharge current, reaches the 3.2V threshold.

Once one of those condition has been accepted as valid the VRPC SM starts the SWITCH ON sequence disregarding any other valid SWITCH ON event. Check VRPC SM flow diagram in lota specification [1].

Sequence consists in:

lota:

- Enabling the main band gap

- Waiting for the Reference Band Gap to reach its nominal value (1.2 V)

- Checking for BG delivering the nominal reference.

- Checking for MB higher than 3.2V

- Enabling RDBB, RABB, RMEM

- Waiting for the LDO's to reach their nominal value.

- Enabling RIO

- Waiting for the LDO to reach its nominal value.

- Release ABB reset and setting the ON\_nOFF signal to logic 1.

If one of the check included in the sequence fails the SM brings system back to OFF state.

## Calypso:

- Waits default RF setup time( 0 at reset).

- Set to logic one the RFEN pin

- Wait default VTCXO setup time (4096 at reset)

- Set to logic one the TCXOEN pin

- Wait SLICER setup time (4096 at reset)

- Enable SLICER module

- Wait 13MHz clock setup time (64 at reset)

## TI – Proprietary Information –

PAGE: 33/81

## Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

- Release the FDP (Flash Deep Power) signal and chip internal reset.

- MCU receives 13 MHz clock after 3 T<sub>VTCXO</sub> (VTCXO periods) and MCU activity starts after 20 T<sub>VTCXO</sub>.

- Program starts:

- SPI access to IOTA :

- Configure lota device

- TSP accesses to RF part :

- Enable Clara LDO's in fast mode

- Configure Clara device

- Configure TSPACT signal.

- Wait for a stable AFC output and nominal regulated output at CLARA LDO's. During this period system enter SW BIG SLEEP mode to avoid power consumption.

- Exit the BIG SLEEP mode.

- Program normal mode in CLARA bandgap.

System is now in ACTIVE state and able to perform GSM activity.

TI – Proprietary Information –

PAGE: 34/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

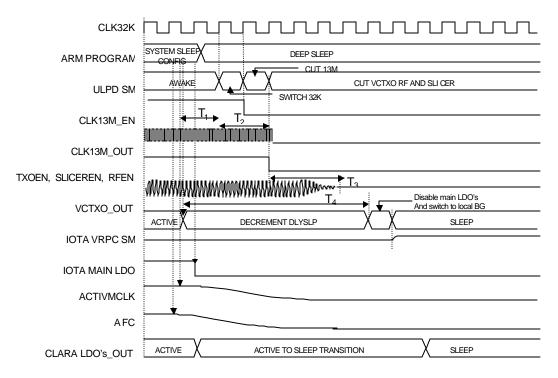

## 5.2.5 SLEEP OFF

lota SLEEP mode has been conceived to support L1 Deep Sleep mode. Deep Sleep mode is a system low power consumption mode configured by L1 SW in which only a small part of the DBB modules keeps their activity on. Those modules are:

- RTC supplied on the VRRTC domain

- XO32K supplied on the VRRTC domain

- ULPD supplied on the VRDBB domain

- INTH<sup>12</sup> supplied on the VRDBB domain.

This mode allows reduction of power consumption during terminal idle mode, or PAGING, in which short periods of GSM activity are alternated with long idle periods.

Application SW puts the system in Deep Sleep once it has evaluated the length in terms of GSM frames in which the terminal is supposed to be inactive. This number of frames is stored in a so called GSM TIMER that starts to be decreased on a frame base once the system enter the Deep Sleep. GSM TIMER activity relies on the 32KHz clock. There are several ways to exit the Deep Sleep mode:

## Synchronous Wake-Up

The GSM TIMER reaches the zero value and wakes up DBB and ABB through an internal interrupt (DBB GSM TIMER IT) and the generation of an ITW AKEUP signal (ABB)

## Asynchronous Wake-Up

DBB is wake-up from an asynchronous event before GSM TIMER interval has been elapsed. Those events generating an internal interrupt to DBB and an external ITWAKEUP signal may be (if non masked interrupts):

- Keypad I/O transition

- RTC alarm

- UART

- EXT\_FIQ

- EXT\_IRQ

push keypad buttons. user pre-programmed alarm out-coming data. INT1 generation due to an EMERGENCY condition External accessory plug, Charger Plug, ON/OFF button push.

SLEEP OFF transition to ACTIVE is generated either by an ITWAKEUP signal going from the DBB to the ABB or by one of the switch on conditions described for the SWITCH ON transition.

This may lead to a double SLEEP OFF request arriving to the ABB. Let us assume that the system is in SLEEP state and that an external accessory is plugged. The edge on RPWRON pin is a valid condition to exit SLEEP mode hence lota starts the SLEEP OFF sequence. This condition will also generate an INT2 to DBB signaling the detection of an edge on the pin.

<sup>12</sup> Interrupt Handler

TI – Proprietary Information –

PAGE: 35/81

Strictly Private

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

If the EXT IRQ is enabled as source of wake-up events in the DBB the ABB will be requested to exit the SLEEP through an ITWAKEUP generation. This new condition does not affect the already started SLEEP OFF sequence. Once again all SLEEP OFF transition are considered valid only if MB voltage value is higher than 3.2V. In the case of a MB lower than 3.2V the system exit the SLEEP mode on a sleep off event but passes directly to BACKUP state. Once a SLEEP OFF condition has been detected:

lota:

- Enables the main band gap

- Waits for the BG to reach its nominal value (1.2 V)

- Checks for BG delivering the nominal reference.

- Checks for MB higher than 3.2V

- Enables RDBB, RABB, RMEM

- Waits for the LDO's reach their nominal value.

- Enables RIO

- Waits for the LDO to reach its nominal value.

If one of the check included in the sequence fails the SM brings system back to OFF state. Iota is then ready to support the system ACTIVE mode.

## Calypso:

- Waits RF setup time(previously programmed in SETUP\_RF\_REG register).

- Set to logic one the RFEN pin

- Wait VTCXO setup time (previously programmed in SETUP\_VCTXO\_REG register)

- Set to logic one the TCXOEN pin

- Wait SLICER setup time (previously programmed in SETUP\_SLICER\_REG register)

- Enable SLICER module

- Wait 13MHz clock setup time (previously programmed in SETUP\_CLOCK\_13MHZ\_REG register)

- Release the FDP (Flash Deep Power) signal and chip internal functional restart

- MCU receives 13 MHz clock after 3 T<sub>VTCXO</sub> (VTCXO periods) and MCU activity starts after 20 T<sub>VTCXO</sub>.

- Program starts:

- SPI access to IOTA :

- Restore lota ACTIVMCLK

- Restore AFC value

- TSP accesses to RF part :

- Enable Clara LDO's in fast mode

- Restore TSPACT configuration.

- Wait for a stable AFC output and nominal regulated output at CLARA LDO's. During this period system enter SW BIG SLEEP mode to avoid power consumption.

- Exit the BIG SLEEP mode.

- Program normal mode in CLARA bandgap.

System is now ready to perform GSM activity.

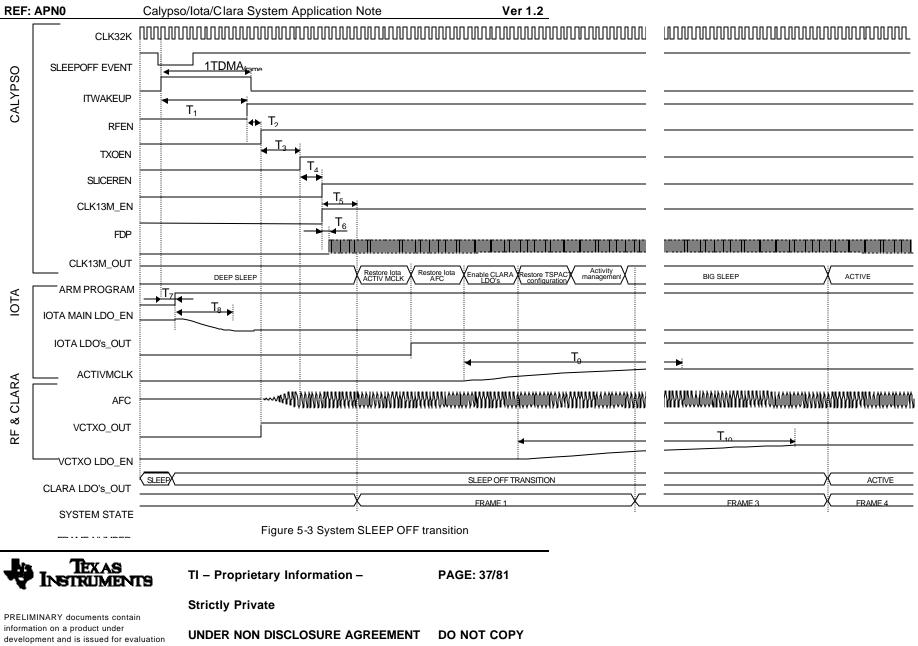

Time diagram in next page summarizes system behavior exiting the SLEEP mode.

**TI – Proprietary Information –**

PAGE: 36/81

**Strictly Private**

PRELIMINARY documents contain information on a product under development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

development and is issued for evaluation purposes only. Features characteristic data and other information are subject to change.

|                                                                       | Min  | Тур              | Max              | Units             | Description                                      |

|-----------------------------------------------------------------------|------|------------------|------------------|-------------------|--------------------------------------------------|

| T <sub>1</sub>                                                        | 1    | 1000             | 4096             | T <sub>32k</sub>  | Setup RF time                                    |

| $T_2$                                                                 | 1    | 31               | 4096             | T <sub>32k</sub>  | Setup VCTXO time                                 |

| $T_3$                                                                 | 1    | 490              | 4096             | T <sub>32k</sub>  | Setup SLICER time                                |

| $\begin{array}{c} T_2 \\ T_3 \\ T_4 \\ T_5 \\ T_6 \\ T_7 \end{array}$ | 1    | 31               | 64               | T <sub>32k</sub>  | Setup CLOCK_13 MHz time                          |

| $T_5$                                                                 |      | 20               |                  | T <sub>TCXO</sub> | Time from FDP high to MCU code execution         |

| $T_6$                                                                 |      | 3                |                  | T <sub>TCXO</sub> | Time from FDP high to 13MHz available to MCU     |

|                                                                       |      | 2                |                  | T <sub>32k</sub>  | Time from ITWAKEUP detection and lota LDO enable |

| T <sub>8</sub>                                                        |      | 151              |                  | T <sub>32k</sub>  | lota main LDO turn on time from SLEEP mode       |

| T <sub>8</sub><br>T <sub>9</sub>                                      | 5 ms |                  | 15               | ms                | AFC setup time                                   |

| T <sub>10</sub>                                                       |      | 10 <sup>13</sup> | 55 <sup>14</sup> | ms                | CLARA LDO turn on time                           |

#### Table 5-1 SLEEP OFF Timing descriptions

The only timing constraint from system point of view is that  $T_8$  lota LDO's turn on time from SLEEP mode needs to be shorter than  $T_1+T_2$ . Is after that time interval, at VCTXO enable, that the system starts to sink more than the SLEEP current from lota LDO's. Thus, at that time, they have to be already able to support ACTIVE mode current.

In current application the RFEN signal is not used. An external LDO enabled by the TXOEN signal provide power supply to the VCTXO

Application SW exiting the Deep Sleep (system SLEEP state) does not need to re-configure Clara device. The Clara serial port is supplied on a lota sleep LDO (RIO) and register contents is maintained even in SLEEP mode.

<sup>&</sup>lt;sup>14</sup> Max value with speed-up disabled