## **Rita Intro**

July,2003

**Texas Instruments Shanghai**

Wireless Customer Integration & Design Center

## Agenda

### • Rita introduction

- 1. Rita architecture

- 2. Receiver

- 3. Transmitter

- 4. Synthesizer

- 5.Regulator

### • **RF-BB** interface

- 1. RF-BB connection

- 2. RF controlling by BB

### • **RF-SW programming and control** *Rita registers introduction*

• Q&A

## **Rita introduction**

1. Rita architecture

2. Receiver

3. Transmitter

4. Synthesizer

5.Regulator

The World Leader In DSP And Analog

3

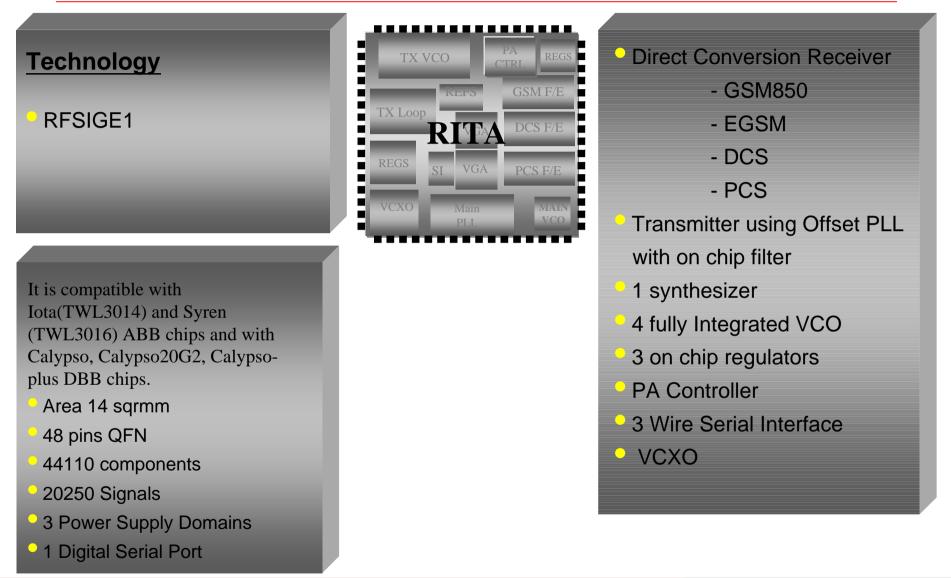

## Migrating from CLARA to RITA

## Clara

- Triple band

- 64Pin,TQFP64,12\*12m m

- Need tank circuits

- Need 2 external VCOs

- Need external VCXO

## Rita

- Quad band

- 48Pin,QFN48,7\*7mm

- Fully-integrated VCO, no need tank circuits

- Including loop filter and VCO

- Including a 26MHz

VCXO with external varactor and crystal

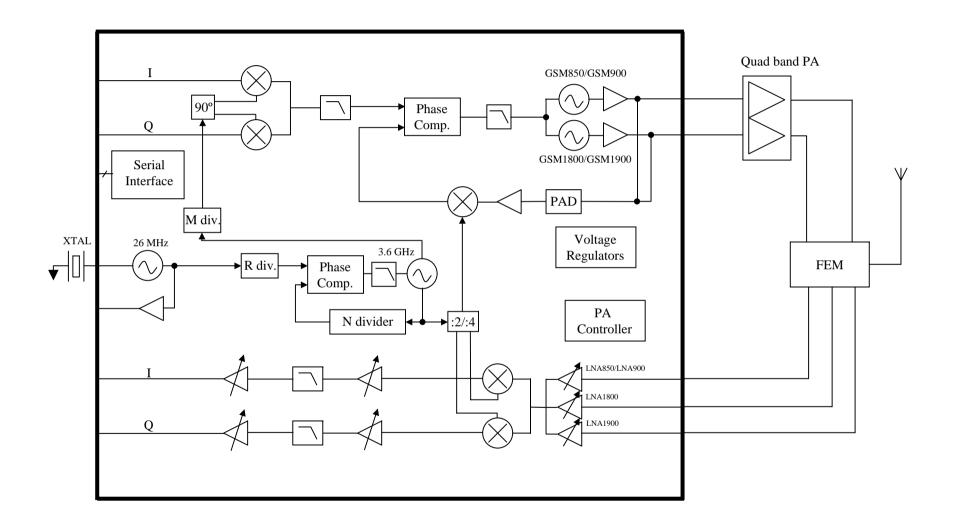

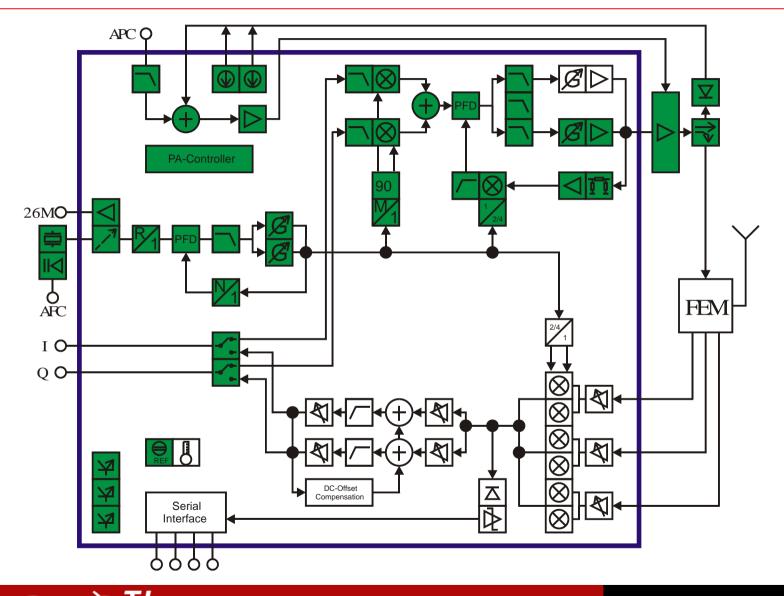

## RITA GSM-GPRS 850/900/1800/1900, RF single chip

### Architecture

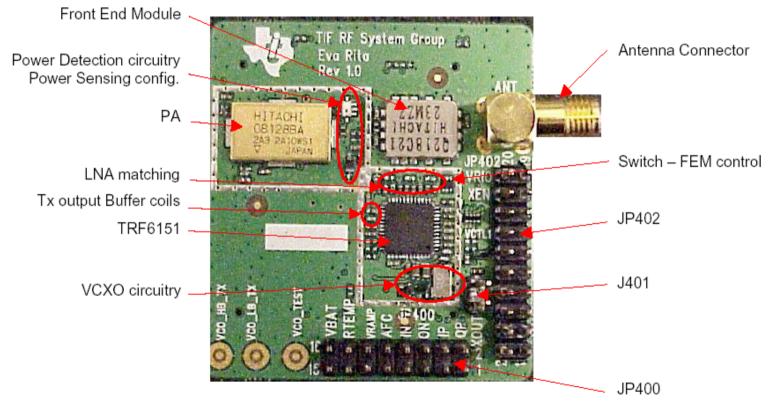

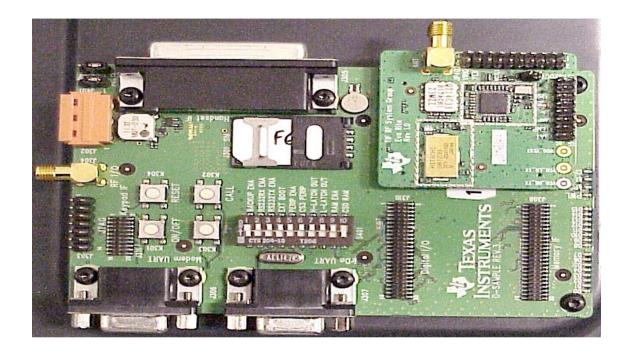

## **Rita EVM**

Can be plugged to: Modified D-Sample

## Modified D-sample

Modifications are to be applied to D-Samples to handle EvaRita Modified D-Sample is dedicated to EvaRita Corresponds to Calypso/Iota/Rita TI chipset

Used to emulate EvaRita in real conditions (GSM TDMA)

Useful to run tests close to the ETSI spec. requirements.

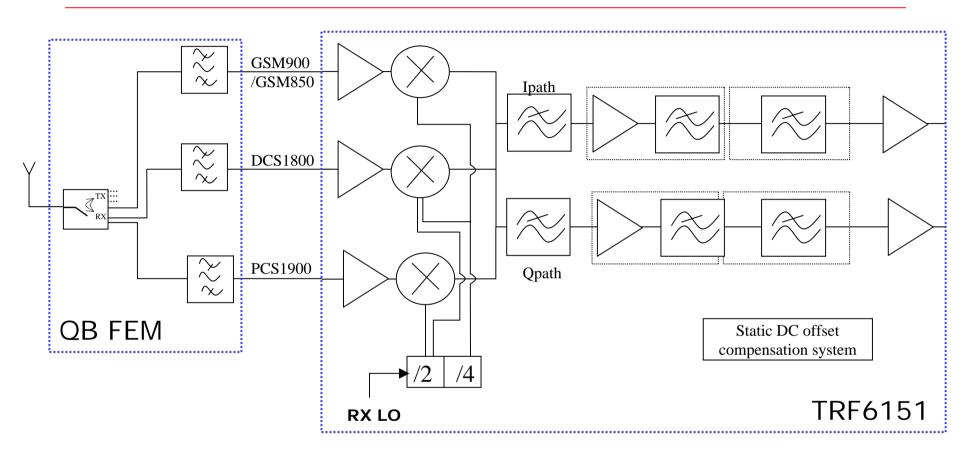

### Receiver

- Direct conversion receiver

- Quad band GSM850+EGSM + DCS + PCS

## Receiver

Receive section:

- - three LNA(LNAGSM/LNADCS/LNAPCS) with switchable gain

- three quadrature demodulators for GSM900/GSM850 (MIXGSM),DCS1800 (MIXDCS) and PCS1900 (MIXPCS) bands with switchable gain

- - two base-band amplifiers with digitally programmable gain

- - two fully integrated base-band channel filters.

- - two DC offset compensation systems

- - a divider by 4 for the LO generation in GSM900 and GSM850 in order to minimize the DC offset generated by self mixing and the LO re-radiation

- - a divider by 2 for the LO generation in DCS1800 and PCS1900 in order to minimize the DC offset generated by self-mixing and the LO reradiation.

### **Receiver Performance**

#### RECEIVER

#### Global performances

| Global perior                                  |                                                                               |        |       |     |      |     |

|------------------------------------------------|-------------------------------------------------------------------------------|--------|-------|-----|------|-----|

| RF input                                       | LNAGSMN/P pins                                                                |        | 869   | -   | 960  | MHz |

| frequency                                      | LNADCSN/P pins                                                                |        | 1805  | -   | 1880 | MHz |

| frequency                                      | LNAPCSN/P pins                                                                |        | 1930  | -   | 1990 | MHz |

| Balanced RF<br>input<br>impedance              | LNAGSMN/P, LNADCSN/P or<br>LNAPCSN/P pins                                     |        | -     | 100 | -    | Ω   |

| RF input return                                | LNAGSMN/P, LNADCSN/P or<br>LNAPCSN/P pins<br>Receiver gain = G_HIGH or G_MID1 |        | -     | -   | -10  | dB  |

| loss                                           | LNAGSMN/P, LNADCSN/P or<br>LNAPCSN/P pins<br>Receiver gain = G_MID2 or G_LOW  |        | -     | -   | -4   | dB  |

|                                                | All bands<br>Front end and VGA high gain mode                                 | G_HIGH | 63    | 66  | 69   | dB  |

| Voltage gain <sup>29</sup>                     | All bands<br>Front end in intermediate gain mode<br>and VGA in high gain mode | G_MID1 | 57    | 60  | 63   | dB  |

| , on age pain                                  | All bands<br>Front end in low gain mode and VGA<br>in high gain mode          | G_MID2 | 43    | 46  | 49   | dB  |

|                                                | All bands<br>Front end and VGA in low gain mode                               | G_LOW  | 17    | 20  | 23   | dB  |

|                                                | LNAGSMN/P pins; G=G_HIGH<br>GSM900 band [925,960Mhz]                          |        | -     | -   | 5    | dB  |

|                                                | LNAGSMN/P pins <sup>31</sup> ; G=G_HIGH<br>GSM850 band [869,894Mhz]           |        | -     | -   | 5.2  | dB  |

| Noise figure <sup>30</sup>                     | LNADCSN/P pins; G=G_HIGH<br>DCS band [1805,1880Mhz]                           |        | -     | -   | 5    | dB  |

|                                                | LNAPCSN/P pins; G=G_HIGH<br>PCS band [1930,1990Mhz]                           |        | -     | -   | 5    | dB  |

|                                                | All bands; $G = G_MID2$                                                       |        | -     | -   | 20.8 | dB  |

| Input 1dB                                      | All bands<br>Gain = $G_HIGH$                                                  |        | -50   | -   | -    | dBm |

| compression                                    | GSM850-GSM900 bands<br>G= G_LOW                                               |        | -19.5 | -   | -    | dBm |

|                                                | DCS1800 - PCS1900 bands<br>$G=G_LOW$                                          |        | -25   | -   | -    | dBm |

| Input 3 <sup>rd</sup> order<br>intercept point | All bands<br>Gain = $G_HIGH^{32}$                                             |        | -20   | -18 | -    | dBm |

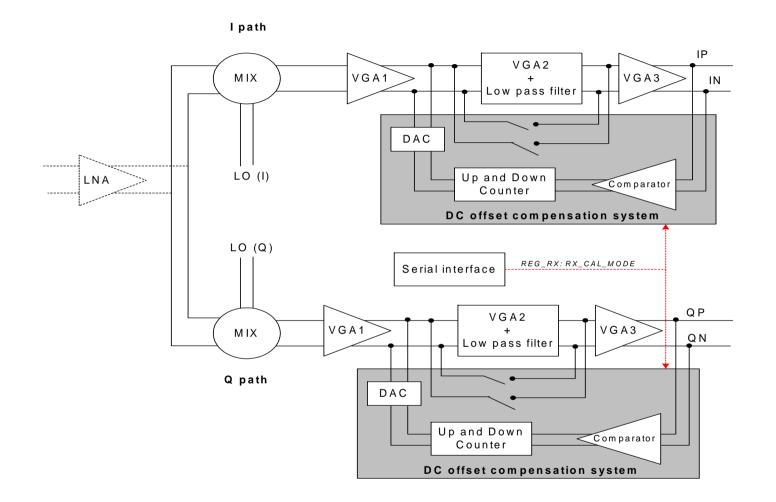

### **DC offset compensation**

- On both I and Q paths, a comparator evaluates the DC offset at receiver output:

- If a positive DC offset is detected, the Up and down counter increments the DCO\_Loop\_register#1.If a negative DC offset is detected, the Up and down counter decrements the DCO\_Loop\_register#1.

- The content of DCO\_Loop\_register#1 is converted to an analog value by the 8-bit DAC:compensation is done at the input of the 2nd stage of the variable gain amplifier and DC offset decreases.

- This compensation circuit acts as a closed loop: As long as a DC offset remains at the receiver output, the DAC reduces the DC offset at the demodulator output.

Texas Instruments

### **Transmitter**

- Transmit section:

- - an offset PLL with post IQ modulator and post offset mixer filters fully integrated on chip

- - two TX VCOs fully integrated on chip

- - a TX loop filter fully integrated on chip

- a divider by 4 for the LO generation in GSM900 and GSM850

- a divider by 2 for the LO generation in DCS1800 and PCS1900

- - a programmable M divider for the IF generation

- - a power amplifier controller including all the functions required to design a power sensing control loop except the sensing diodes

## Tx performance

#### TRANSMITTER

#### **Transmitter inputs**

| I/Q inputs common<br>mode voltage |                    | 1.215 | 1.35 | 1.485 | V   |

|-----------------------------------|--------------------|-------|------|-------|-----|

| I/Q inputs voltage<br>swing       | Single ended       | 0.44  | 0.47 | 0.49  | Vpp |

| I/Q inputs resistance             | Differential ended | 10    |      |       | kO  |

| I/Q inputs<br>capacitance         | Differential ended |       |      | 25    | pF  |

#### Low Band Output

Dedicated to GSM850 and E-GSM900

GMSK modulated signal applied at the IQ inputs (unless otherwise specified)

| Frequency range    |                                               | fout | 824.2 to |     |         | MHz    |

|--------------------|-----------------------------------------------|------|----------|-----|---------|--------|

|                    |                                               |      | 914.8    |     |         |        |

| Output impedance   |                                               | Zout |          | 50  |         | 0      |

| Output Return Loss |                                               |      |          |     | -10     | dB     |

| Output power level | into 50 O load                                | Pout | 4        | 6   | 8       | dBm    |

| Phase error        | Max. RMS phase error<br>Max. Peak phase error |      |          |     | 3<br>10 | degree |

| TXVCOLB Pulling    | VSWR= 2, all phases,<br>open loop             | PULL |          | tbd |         | MHz    |

## Tx performance (cont.)

#### Spurious emissions<sup>25</sup>

#### Specification at the antenna with the use of the TBD PA and the TBD FEM

#### E-GSM 900

|                      | from 9 kHz to 1 GHz         |  | -69  | dBe |

|----------------------|-----------------------------|--|------|-----|

| level when allocated | from 1 GHz to 12.75 GHz     |  | -63  | dBe |

| channel              | in the band [925 ~ 935 MHz] |  | -100 | dBc |

|                      | in the band [935 ~ 960 MHz] |  | -112 | dBc |

|                      | in the band [1805 ~ 1880    |  | -104 | dBc |

|                      | MHz]                        |  |      |     |

|                      | in the bands [1900 ~1920    |  | -99  | dBc |

|                      | MHz], [1920 ~ 1980 MHz],    |  |      |     |

|                      | [2010 ~ 2025 MHz] and       |  |      |     |

|                      | [2110 ~ 2170 MHz]           |  |      |     |

#### DCS 1800

|         | from 9 kHz to 1 GHz         |  | -66  | dBc |

|---------|-----------------------------|--|------|-----|

|         | from 1 GHz to 12.75 GHz     |  | -60  | dBc |

| channel | in the band [925 ~ 935 MHz] |  | -97  | dBc |

|         | in the band [935 ~ 960 MHz] |  | -109 | dBc |

|         | in the band [1805 ~ 1880    |  | -101 | dBc |

|         | MHz]                        |  |      |     |

|         | in the bands [1900 ~1920    |  | -96  | dBe |

|         | MHz], [1920 ~ 1980 MHz],    |  |      |     |

|         | [2010 ~ 2025 MHz] and       |  |      |     |

|         | [2110 ~ 2170 MHz]           |  |      |     |

#### GSM 850

|                      | from 9 kHz to 1 GHz         |  | -69  | dBe |

|----------------------|-----------------------------|--|------|-----|

| level when allocated | from 1 GHz to 12.75 GHz     |  | -63  | dBe |

| channel              | in the band [869 ~ 894 MHz] |  | -112 | dBe |

|                      | in the band [1930 ~ 1990    |  | -104 | dBe |

|                      | MHz]                        |  |      |     |

#### PCS 1900

|                      | from 9 kHz to 1 GHz         |  | -66  | dBc |

|----------------------|-----------------------------|--|------|-----|

| level when allocated | from 1 GHz to 12.75 GHz     |  | -60  | dBe |

| channel              | in the band [869 ~ 894 MHz] |  | -109 | dBe |

|                      | in the band [1930 ~ 1990    |  | -101 | dBc |

|                      | MHz]                        |  |      |     |

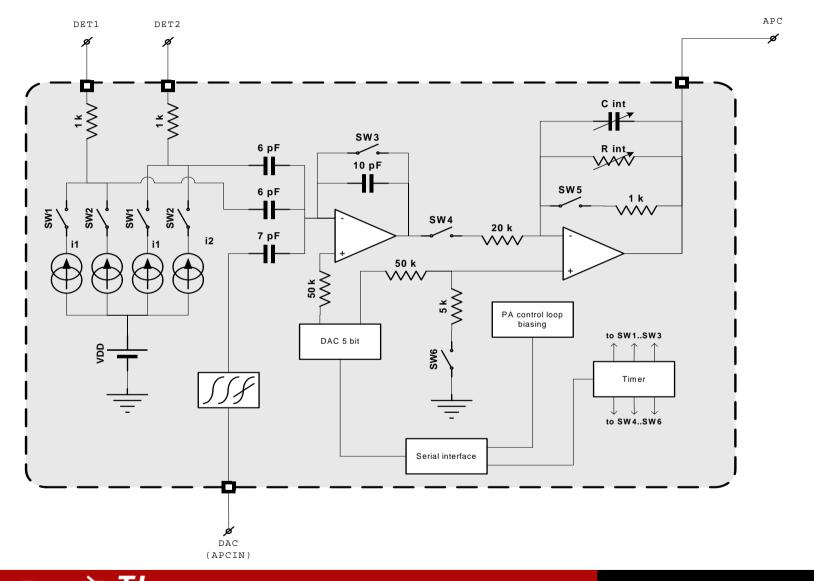

### **PA Controller**

The World Leader In DSP And Analog

### PA controller register

#### REG\_PWR register

| Bit | Name         | Description                                                                                     | Value at reset |

|-----|--------------|-------------------------------------------------------------------------------------------------|----------------|

| 15  | PACTLR_APCEN | <ul><li>0: PA controller is disabled<sup>75</sup></li><li>1: PA controller is enabled</li></ul> | 0              |

| 14  | PACTLR_APC   | <b>0:</b> PA controller is OFF <b>1:</b> PA controller is ON                                    | 0              |

#### REG\_CFG register

| 13:12 | PACTLR_CAP   | <b>00:</b> 0 pF<br><b>01:</b> 12.5 pF<br><b>11:</b> 25 pF<br><b>10:</b> 50 pF                                                                                                 | 10    |

|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 11:10 | PACTLR_RES   | <ul> <li>00: open</li> <li>01: 150 kΩ</li> <li>10: 300 kΩ</li> <li>11: not used</li> </ul>                                                                                    | 10    |

| 9:5   | PACTLR_VHOME | PA controller detection voltage setting: 1<br>00000:0*Vstep+Vlow ~ 0.46 V<br>00001:1*Vstep+Vlow ~ 0.49 V<br>00010: 2*Vstep+Vlow ~ 0.52 V<br><br>11111: 31*Vstep+Vlow ~ 1.39 V | 01100 |

| 4     | PACTLR_IDIOD | <ul><li>0: Diode bias current is low (30 uA)</li><li>1: Diode bias current is high (300 uA)</li></ul>                                                                         | 0     |

| 3     | PACTLR_TYPE  | <ul><li>0: Power sensing</li><li>1: Current sensing (for test purpose only)</li></ul>                                                                                         | 0     |

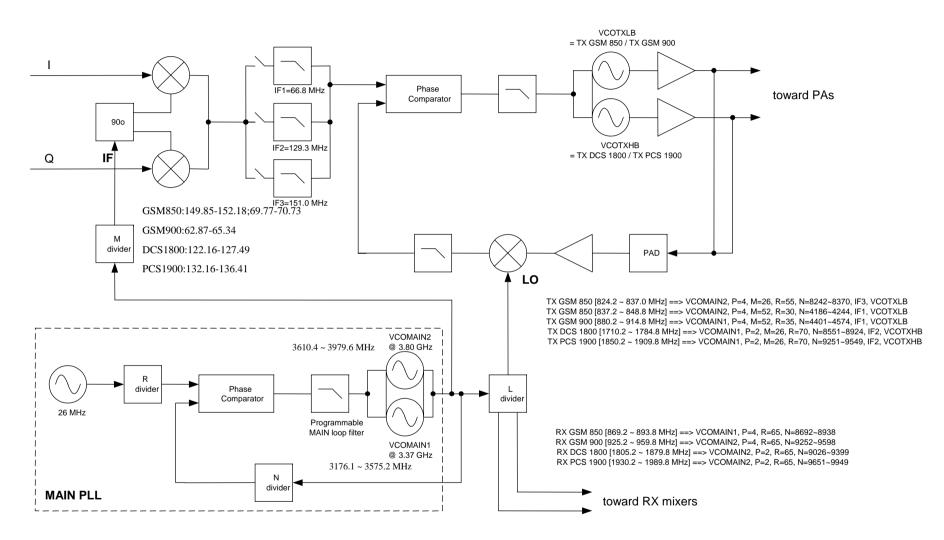

### **Synthesizer**

The World Leader In DSP And Analog

TEXAS INSTRUMENTS

Four VCOs are used :

- a TX LB VCO [824.2 ~ 914.8 MHz] to generate the TX GSM 850 / TX GSM 900,

- a TX HB VCO [1710.2 ~ 1909.8 MHz] to generate the TX DCS 1800 / TX PCS 1900,

- a MAIN VCO 1 [3176.1 ~ 3575.2 MHz] (see below) to generate the RX GSM 850 / LO

(and IF) for TX GSM 900, TX DCS 1800 and TX PCS 1900,

- a MAIN VCO 2 [3610.4 ~ 3979.6 MHz] (see below) to generate the RX GSM 900 / RXDCS 1800 / RX PCS 1900 / LO (and IF) for the two parts of TX GSM 850.

## Synthesizer

| Parameters | Test conditions | Symbol | Min. | Тур. | Max. | Unit |

|------------|-----------------|--------|------|------|------|------|

|------------|-----------------|--------|------|------|------|------|

### Reference clock input<sup>17</sup>

| Input frequency       |                |     | 26  |       | MHz    |

|-----------------------|----------------|-----|-----|-------|--------|

| Input sensitivity     |                | 0.5 | 1.0 | 2.0   | Vpp    |

| Reference phase noise | @ 1 kHz offset |     |     | -129  | dBc/Hz |

| Duty cycle            |                |     |     | 40/60 |        |

|                       |                |     |     | to    |        |

|                       |                |     |     | 60/40 |        |

| Input resistance      |                | 10  |     |       | kΩ     |

| Input capacitance     |                |     |     | 5     | pF     |

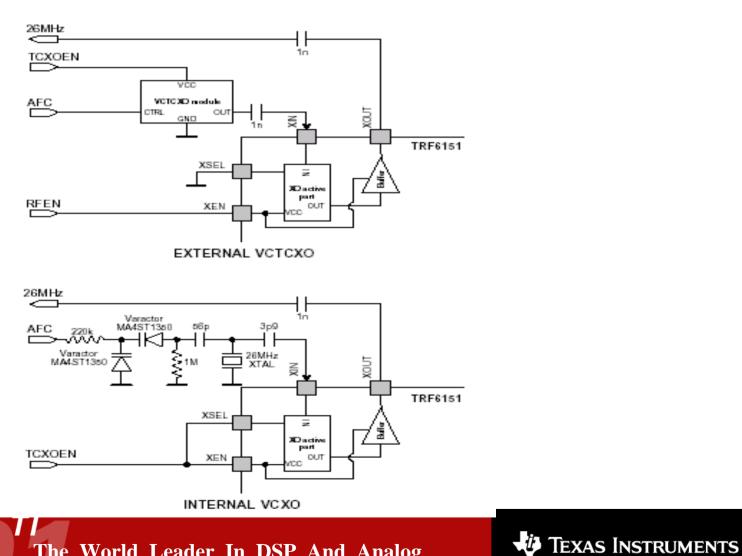

### VCXO buffer output (XOUT pin)<sup>18</sup>

| Output frequency |  |     | 26  |     | MHz |

|------------------|--|-----|-----|-----|-----|

| Output level     |  | 0.5 | 1.0 | 2.0 | Vpp |

| Crystal and External V                        |                                                                |    | 2.4   | 1            | 2.0          | 17         |

|-----------------------------------------------|----------------------------------------------------------------|----|-------|--------------|--------------|------------|

| XEN supply pin                                | (a) I = 3.2mA                                                  |    | 2.4   |              | 2.9          | V          |

| Crystal                                       |                                                                |    |       |              |              |            |

| Nominal frequency                             |                                                                |    |       | 26.0         |              | MHz        |

| Frequency tolerance                           | at 25° C±3°C                                                   |    |       |              | ±10.0        | ppm        |

| Temperature<br>characteristics                | in reference to $+25^{\circ}C$<br>over $-20 \sim +75^{\circ}C$ |    |       |              | ±10.0        | ppm        |

| Aging 1 <sup>st</sup> year<br>after 5 years   |                                                                |    |       |              | ±1.0<br>±2.5 | ppm<br>ppm |

| Dips vs. temperature                          | −20 ~ +75°C                                                    |    |       |              | 0.3          | ppm/°C     |

| Frequency versus<br>temperature slope at 25°C | at 25° C $\pm$ 7°C                                             |    | -0.5  |              | 0            | ppm/°C     |

| Equivalent Series<br>Resistance               |                                                                |    | 0     |              | 40           | Ω          |

| Standard load capacitance                     |                                                                |    |       | 9.3<br>(tbc) | 12.0         | pF         |

| Shunt capacitance                             |                                                                |    |       | 1.5          | 1.7          | pF         |

| Motional capacitance                          |                                                                |    | 5.4   | 6.3          | 7.2          | fF         |

| Drive level                                   |                                                                |    |       |              | 150          | μW         |

| Varactor network                              |                                                                |    |       |              |              |            |

| Minimum voltage tuning                        |                                                                | Vt | 0     |              | 2.0          | V          |

| Tuning range                                  | with $Vt = 0V$ to 2.0V                                         |    | ±26.0 | ±33.0        | ±41.0        | ppm        |

| Sensitivity accuracy <sup>15</sup>            | Over temp and over<br>the tuning range                         |    |       |              | 20 %         | Hz/step^2  |

| Frequency step                                |                                                                |    |       |              | 0.01         | ppm/step   |

#### Crystal and External Varactor network <sup>14</sup>

| specification at the mix  | leis LO port             |      |      |      |        |

|---------------------------|--------------------------|------|------|------|--------|

| Prescaler input frequency |                          | 3476 |      |      | MHz    |

| range                     |                          | to   |      |      |        |

|                           |                          | 3840 |      |      |        |

| PFD operating frequency   |                          |      | 400  |      | kHz    |

| N divider ratio           |                          | 8692 |      |      |        |

|                           |                          | to   |      |      |        |

|                           |                          | 9598 |      |      |        |

| L divider by 4 output     |                          | 869  |      |      | MHz    |

| frequency range           |                          | to   |      |      |        |

| 1 9 8                     |                          | 960  |      |      |        |

| Close in phase noise      | @ 1 kHz offset           |      | -90  | -81  | dBc/Hz |

|                           | fcomp = 400  kHz         |      |      |      |        |

|                           | @ 960 MHz                |      |      |      |        |

| Phase noise               | @ 600 kHz offset         |      | -130 | -120 | dBc/Hz |

|                           | a 1.6 MHz offset         |      |      | -135 |        |

|                           | a 3.0 MHz offset         |      |      | -140 |        |

|                           | a 10 MHz offset          |      |      | -142 |        |

|                           | @ 20 MHz offset          |      |      | -145 |        |

| Reference feedthrough     | @ 400 kHz offset         |      | -80  | -53  | dBc    |

| -                         | a 800 kHz offset         |      | -94  | -68  |        |

|                           | @ 1.6 MHz offset         |      |      | -79  |        |

| Lock time                 | 1) GSM850:               |      | 100  | 170  | us     |

|                           | From 869MHz to 894MHz    |      |      |      |        |

|                           | 2) GSM900:               |      |      |      |        |

|                           | From 925MHz to 960MHz    |      |      |      |        |

|                           | 3) PCS1900 → GSM850:     |      |      |      |        |

|                           | From 1990MHz to 869MHz   |      |      |      |        |

|                           | 4) DCS1800 → GSM900:     |      |      |      |        |

|                           | From 1880MHz to 925MHz   |      |      |      |        |

|                           |                          |      |      |      |        |

|                           | @ 20 Hz averaged         |      |      |      |        |

|                           | frequency error over one |      |      |      |        |

|                           | burst                    |      |      |      |        |

#### Main synthesizer in RX mode for GSM 850 and E-GSM 900

Specification at the mixers LO port

## Voltage regulators

#### VOLTAGE REGULATION

C<sub>out</sub>=1.0uF, C<sub>bandgap</sub>=100nF unless otherwise specified.

Table specifies regulator and bandgap together unless otherwise specified.

If an external regulation is desired, the internal voltage regulators can be bypassed (regulators shut down).

#### Band gap

| Turn-on time        | speed up mode active |  |    | 25 | ms |

|---------------------|----------------------|--|----|----|----|

| Consumption current |                      |  | 80 |    | uA |

#### Regulator R1

| Input voltage        |                             | Vin     | 3.0 <sup>4</sup> | 3.6 | 5.5 | V     |

|----------------------|-----------------------------|---------|------------------|-----|-----|-------|

| Output voltage       | @ Ioutmax                   | Vout    | 2.7              | 2.8 | 2.9 | V     |

| Max. output current  |                             | Ioutmax | 60               |     |     | mA    |

| Ground pin current   | @ Ioutmax                   |         |                  |     | 6.0 | mA    |

|                      | a Iout = 0 mA               |         |                  |     | 0.3 |       |

| DC line regulation   | From Vinmin to Vinmax       |         |                  |     | 50  | mV    |

|                      | @ Ioutmax                   |         |                  |     |     |       |

| AC line regulation   | Vin step from Vout + 0.1    |         |                  |     |     | mV    |

| Overshoot            | to Vout + 0.5 in 30 us      |         |                  |     | 20  |       |

| Undershoot           | Vin step from Vout + 0.5    |         |                  |     | 20  |       |

|                      | to Vout + 0.1 in 30 us      |         |                  |     |     |       |

| DC load regulation   | Iout = 0 mA to Ioutmax      |         |                  |     | 50  | mV    |

| AC load regulation   | Iout step from Ioutmax to   |         |                  |     |     | mV    |

| Overshoot            | Ioutmax/2 in 5 us           |         |                  |     | 30  |       |

| Undershoot           | Iout step from Ioutmax/2 to |         |                  |     | 30  |       |

|                      | Ioutmax in 5 us             |         |                  |     |     |       |

| Output voltage noise | f =10 Hz to 100 kHz         |         |                  | 50  |     | uVrms |

|                      | Iout = Ioutmax              |         |                  |     |     |       |

|                      | Vin = Vout + 0.2 V          |         |                  |     |     |       |

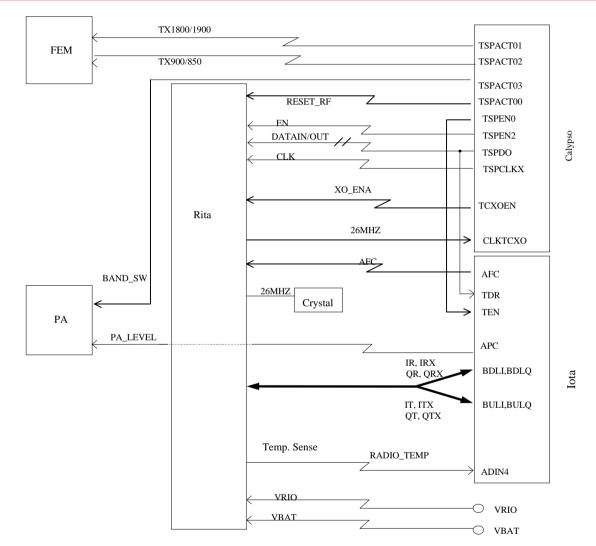

## **RF-BB interface**

- 1. RF-BB connection

- 2. RF controlling by BB

(grow)<sup>*TI*</sup> The World Leader In DSP And Analog

### **RF-BB** connection

## RF controlling by BB

- Auto Frequency Control

- Auto Power Control

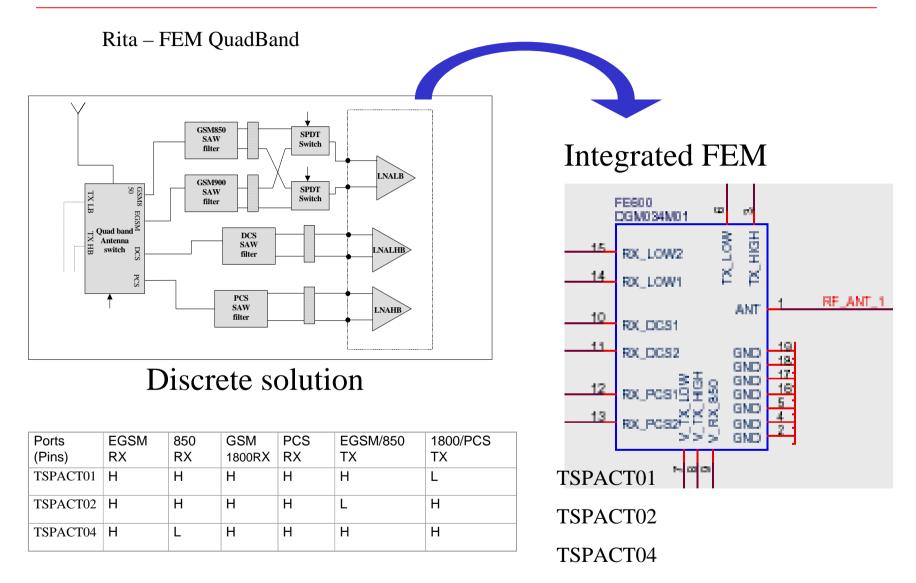

- FEM control

## AFC (Auto Frequency Control)

AFC's purpose is to correct frequency shifts of the voltage-controlled oscillator to ٠ maintain the master clock frequency in a 0.1-PPM range

## APC(Automatic Power Control)

- The automatic power control (APC) generates an envelope signal to control the power ramp up, power ramp down, and power level of the radio burst. The APC structure is intended to support single-slot and multislot transmission with smooth power transition when consecutive bursts are transmitted at different power levels.

- Refer to the PA controller loop.

## **RF control-FEM Control**

TEXAS INSTRUMENTS

# **RF-SW programming and control**

1. Rita registers introduction

## **Rita registers introduction**

### SERIAL INTERFACE PROGRAMMING

#### Serial word format

٠

| MS        | SB        |           |           |           |           |          |          |          |          |          |          |          |          | Ι        | SB       |

|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| FIF       | RST       | IN        |           |           |           |          |          |          |          |          |          |          | L        | AST      | IN       |

| Bit<br>15 | Bit<br>14 | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit<br>9 | Bit<br>8 | Bit<br>7 | Bit<br>6 | Bit<br>5 | Bit<br>4 | Bit<br>3 | Bit<br>2 | Bit<br>1 | Bit<br>0 |

#### **Registers table**

| Α | ddre | SS | Serial word format | Register name | Definition                                           |

|---|------|----|--------------------|---------------|------------------------------------------------------|

| 0 | 0    | 0  | 16 bits            | REG_RX        | RF general settings                                  |

| 0 | 0    | 1  | 16 bits            | REG_PLL       | PLLs settings                                        |

| 0 | 1    | 0  | 16 bits            | REG_PWR       | Power on/off all functional block of the transceiver |

| 0 | 1    | 1  | 16 bits            | REG_CFG       | Transceiver config, PA Controller setting            |

| 1 | 0    | 0  | 16 bits            | REG_TEST1     |                                                      |

| 1 | 0    | 1  | 16 bits            | REG_TEST2     | Reserved for test <sup>70</sup>                      |

| 1 | 1    | 0  | 16 bits            | REG_TEST3     | Reserved for test                                    |

| 1 | 1    | 1  | 16 bits            | REG_TEST4     |                                                      |

## REG\_RX

This register is used to configure the receiver, to launch RX calibration process

| Bit   | Name                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                   | Value at<br>reset |

|-------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 15:11 | VGA_GAIN                  | 00000 - 00101: reserved<br>00110: VGA gain =14dB<br>00111: VGA gain =16 dB<br>01000: VGA gain =18 dB<br>01001: VGA gain =20 dB<br>01010: VGA gain =22 dB<br>01011: VGA gain =24 dB<br>01100: VGA gain =26 dB<br>01101: VGA gain =28 dB<br>01110: VGA gain =30 dB<br>01111: VGA gain =32 dB<br>10000: VGA gain =34 dB<br>10001: VGA gain =36 dB<br>10010: VGA gain =38 dB<br>10011: VGA gain =40 dB<br>10100 - 11111: reserved | 10011             |

| 10:9  | RF_GAIN                   | 00: low RF gain (GRF_LOW)<br>01: reserved<br>10: reserved<br>11: high RF gain (GRF_HIGH)                                                                                                                                                                                                                                                                                                                                      | 11                |

| 8     | RX_CAL_MODE <sup>76</sup> | <ul> <li>0: Stop RX calibration process</li> <li>1: power on DC offset calibration system and start RX calibration process.</li> </ul>                                                                                                                                                                                                                                                                                        | 0                 |

| 7     | READ_EN                   | <ul><li>0: Data serialized on SIOUT pin are 0</li><li>1: Data serialized on SIOUT pin are REG_RX content</li></ul>                                                                                                                                                                                                                                                                                                            | 0                 |

| 6     | Reserved                  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                 |

| 5     | Reserved                  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                 |

| 4     | Reserved                  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                 |

| 3     | Reserved                  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                 |

## REG\_PLL

This register is used to program the synthesizer frequency according the desired

#### RX/TX channel.

|               | •                                 | reset   |

|---------------|-----------------------------------|---------|

| 15:9 PLL_REGB | $B = [64; 66; 67 \dots 155]^{69}$ | 0000000 |

| 8:3 PLL_REGA  | A = [0; 1; 263]                   | 000000  |

Useful formulas for synthesizers are:

| Useful formul        | as for | syntne | sizers | are: |            |         |                                                                |

|----------------------|--------|--------|--------|------|------------|---------|----------------------------------------------------------------|

|                      | Р      | R      | L      | М    | B range    | A range | RX/TX RF Frequency (MHz)                                       |

| RX<br>Low band       | 64     | 65     | 4      | -    | [135; 150] | [0; 62] | $\frac{(B*P+A)}{26}$                                           |

| RX<br>High band      | 64     | 65     | 2      | -    | [141; 155] | [0; 63] | R*L 20                                                         |

| TX mode<br>GSM850_1  | 64     | 55     | 4      | 26   | [128; 130] | [0; 62] | $(\frac{1}{A} - \frac{1}{A}) * \frac{(B * P + A)}{A} * 26$     |

| TX mode<br>GSM850_2  | 64     | 30     | 4      | 52   | [65; 66]   | [0; 63] | $\left(\frac{1}{L} - \frac{1}{M}\right)^{-1} = \frac{1}{R}$    |

| TX mode<br>GSM900    | 64     | 35     | 4      | 52   | [68; 71]   | [0; 63] | $(\frac{1}{L} + \frac{1}{M}) * \frac{(B*P+A)}{R} * 26$         |

| TX mode High<br>band | 64     | 70     | 2      | 26   | [133; 149] | [0; 63] | $\left(\frac{1}{L}, \frac{1}{M}\right)^{\prime} = \frac{1}{R}$ |

## **REG\_PWR**

This register is used to power on/off all functional block of the transceiver and to choose the RX/TX band.

| Bit   | Name                      | Description                                                                                                                                                                                                                                               | Value<br>at<br>reset |

|-------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15    | PACTLR_APCEN              | 0: PA controller is disabled <sup>70</sup><br>1: PA controller is enabled                                                                                                                                                                                 | 0                    |

| 14    | PACTLR_APC                | 0: PA controller is OFF <sup>70</sup><br>1: PA controller is ON                                                                                                                                                                                           | 0                    |

| 13    | TX_MODE                   | 0: Transmitter is OFF<br>1: Transmitter is ON                                                                                                                                                                                                             | 0                    |

| 12:11 | RX_MODE                   | <ul> <li>00: Receiver +interferer detection system are OFF</li> <li>01: Receiver is ON (RX mode A)</li> <li>10: Receiver +interferer detection system is ON (RX mode B1)</li> <li>11: Receiver +interferer detection system is ON (RX mode B2)</li> </ul> | 00                   |

| 10:9  | SYNTHE_MODE <sup>71</sup> | <ul> <li>00: Synthesizer, transmitter and receiver are off</li> <li>01: RX Synthesizer is ON</li> <li>10: TX Synthesizer is ON</li> <li>11: not used</li> </ul>                                                                                           | 00                   |

| 8:6   | BAND                      | 000-001: GSM900<br>010-011: DCS<br>100: GSM850 (Low part)<br>101: GSM850 (High part)<br>110-111: PCS                                                                                                                                                      | 000                  |

| 5     | REGUL_MODE                | 0: Regulators are OFF<br>1: Regulators are ON                                                                                                                                                                                                             | 0                    |

| 4:3   | BANDGAP_MODE              | <ul> <li>00-01: Band gap is OFF</li> <li>10: Band gap is ON; speed up mode is enabled</li> <li>11: Band gap is ON; speed up mode is disabled</li> </ul>                                                                                                   | 00                   |

## REG\_CFG

ΤΙ

This register is used to configure the transceiver and set the PA controller at mobile

initialization.

| Bit   | Name         | Description                                                                                                                                                                               | Value at<br>reset |

|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 15    |              | Not used                                                                                                                                                                                  | -                 |

| 14    | TEMP_SENSOR  | 0: Temperature sensor is OFF<br>1: Temperature sensor is ON                                                                                                                               | 0                 |

| 13:12 | PACTLR_CAP   | 00:0 pF<br>01:12.5 pF<br>10:25 pF<br>11:50 pF                                                                                                                                             | 10                |

| 11:10 | PACTLR_RES   | 00: open<br>01: 150 kΩ<br>10: 300 kΩ<br>11: not used                                                                                                                                      | 10                |

| 9:5   | PACTLR_VHOME | PA controller detection voltage setting: <sup>72</sup><br>00000:0*Vstep+Vlow ~ 0.46 V<br>00001:1*Vstep+Vlow ~ 0.49 V<br>00010: 2*Vstep+Vlow ~ 0.52 V<br><br>11111: 31*Vstep+Vlow ~ 1.39 V | 01100             |

| 4     | PACTLR_IDIOD | 0: Diode bias current is low (30 uA)<br>1: Diode bias current is high (300 uA)                                                                                                            | 0                 |

| 3     | PACTLR_TYPE  | 0: Power sensing<br>1: Current sensing (for test purpose only)                                                                                                                            | 0                 |

## **Q&A**

(grow)

## Thank you!